# Databus Products

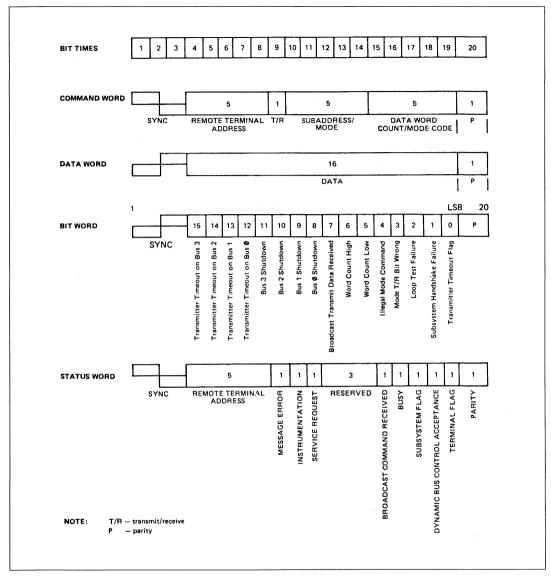

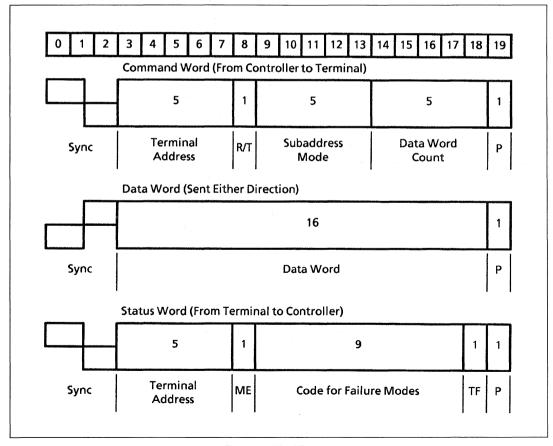

# Handbook

January 1992

GEC PLESSEY

# DATABUS PRODUCTS

Handbook

MIL-STD-1553 MIL-STD-1397 Fibre Optics

GEC PLESSEY

SEMICONDUCTORS

# Contents

|                     |                            | Page         |

|---------------------|----------------------------|--------------|

| Forward             |                            | (iv)         |

| Product Lists       |                            | (v)          |

| Section 1: Comple   | ete Terminals              | 1-1 to 1-90  |

| Section 2: Driver/I | Receivers (Transceivers)   | 2-1 to 2-30  |

| Section 3: Transc   | eiver/Protocol             | 3-1 to 3-18  |

| Section 4: Protoc   | ol                         | 4-1 to 4-102 |

| Section 5: Sub-Sy   | stem Interfaces            | 5-1 to 5-10  |

| Section 6: Encode   | er/Decoders                | 6-1 to 6-26  |

| Section 7: Card P   | roducts                    | 7-1 to 7-24  |

| Section 8: Mil-Std  | -1397                      | 8-1 to 8-36  |

| Section 9: Mil-Std  | -1773 Fibre Optic Products | 9-1 to 9-6   |

| Section 10: GPS L   | ocations                   | 10-1 to 10-8 |

#### Foreword

This handbook brings together for the first time in one document, data on the MIL-STD-1553 and associated bus standard components, manufactured by the former MEDL Hybrid and IC groups, along with those from the former MCTC (CTI) organisation.

For over 12 years the organisation has been a world leader in data bus products, pioneering one of the first LSI Silicon implementations of the protocol function, and introducing the first Transceivers to the market as standard products.

In addition the databook contains information on a unique range of MIL-STD-1397 (STANAG 4153) Products, including fibre optic implementations.

Our current range contains products to fulfil a whole range of different applications. If your needs are not met by our products, let us know!

#### Please Note:

- 1. Certain earlier products which are still available are not listed for space reasons.

- 2. Radiation Hard SOS MIL-STD-1553 products from GPS are listed in sister publication SOS Radiation Hard Handbook (S00000FDB Issue 1).

Please consult your nearest Service Centre or representative for information on either of the above.

# **Product List - Complete Terminals**

| Type No.     | Description                                                                                                                                            | Package                                    | Voltage             | Page |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|------|

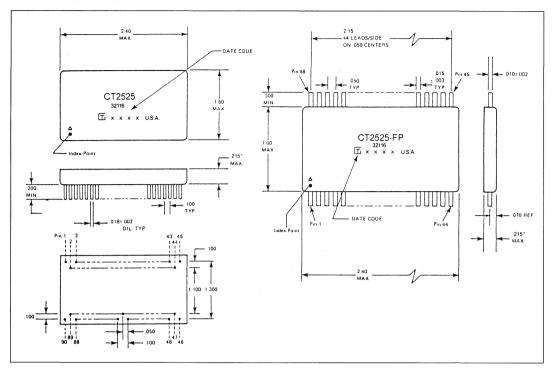

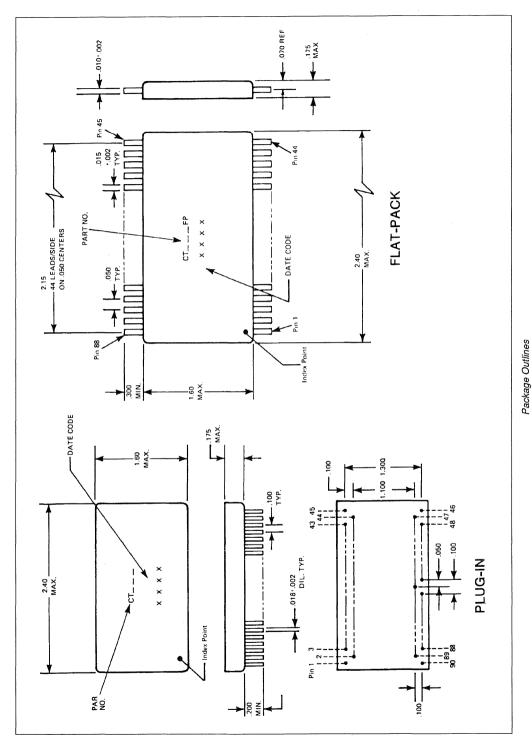

| CT2525       | R.T/B.C. MIL-STD-1553B Dual Transceiver                                                                                                                | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V, ±15V           | 1-3  |

| CT2526       | R.T/B.C. MIL-STD-1553B Dual Transceiver                                                                                                                | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V, ±12V           | 1-3  |

| CT2527       | R.T/B.C. MIL-STD-1553B Dual Transceiver                                                                                                                | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V                 | 1-3  |

| CT2528       | R.T/B.C. MIL-STD-1553B                                                                                                                                 | 90 Pin Plug-In*                            | +5V                 | 1-3  |

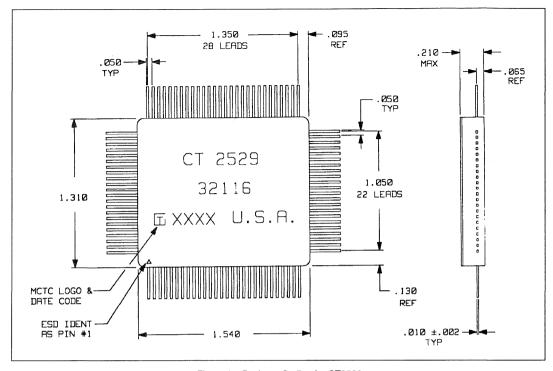

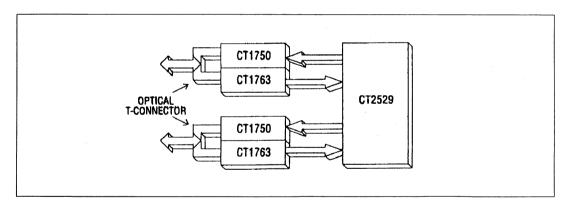

| CT2529       | R.T/B.C. MIL-STD-1553B<br>Small outline package.                                                                                                       | 100 Pin<br>Quad Flat Pack<br>1.54" x 1.32" | +5V                 | 1-3  |

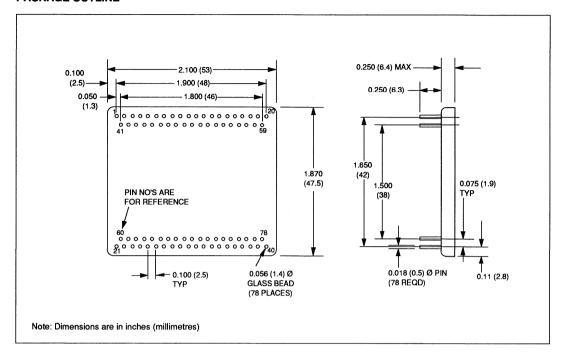

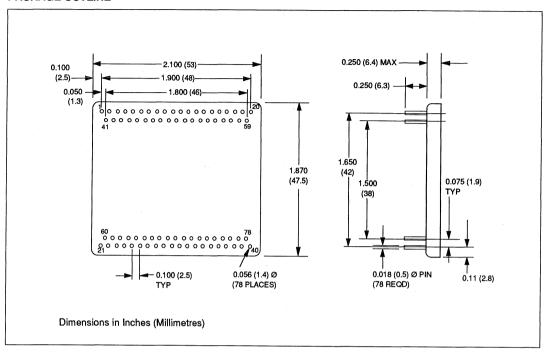

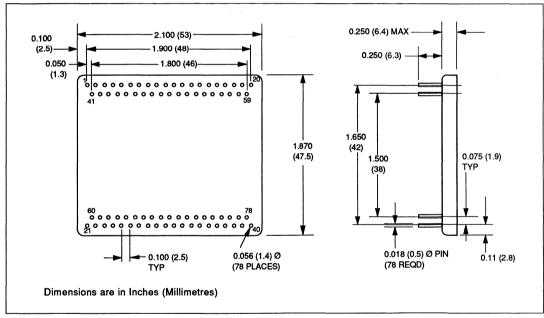

| CT2553       | R.T./B.C. MIL-STD-1553B<br>Pin compatible to BUS61553.                                                                                                 | 78 Pin<br>Quad Plug-In<br>2.1" x 1.87"     | +5V, -15V           | 1-35 |

| CT2554       | R.T./B.C. MIL-STD-1553B<br>Pin compatible to BUS61554.                                                                                                 | 78 Pin<br>Quad Plug-In<br>2.1" x 1.87"     | +5V, -12V           | 1-35 |

| CT2555       | R.T./B.C. MIL-STD-1553B<br>Pin compatible to BUS61555.                                                                                                 | 78 Pin<br>Quad Plug-In<br>2.1" x 1.87"     | +5V                 | 1-35 |

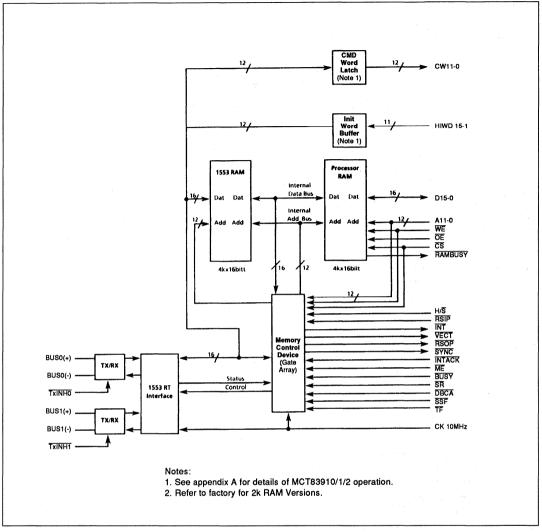

| MCT83102/3/5 | R.T.U. with sub system interface and dual port double buffered RAM.                                                                                    | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V, ±15V†<br>±12V† | 1-47 |

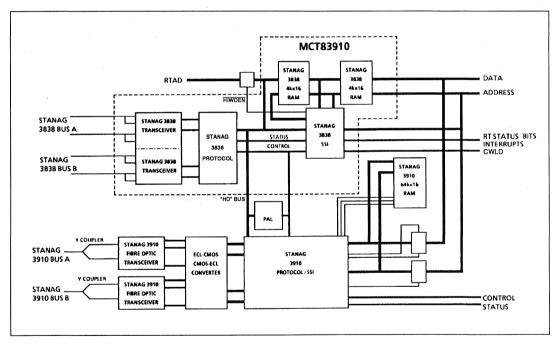

| MCT83910     | R.T.U. with interface, 4K RAM, +5V/±15V transceiver. Similar to MCT83100 Series but for use in STANAG 3910 applications, along with HS data link chip. | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V, ±15V†          | 1-47 |

| MCT83911     | As MCT83910 but with +5V/±12V supply option.                                                                                                           | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V, ±12V†          | 1-47 |

| MCT83912     | As MCT83911 but with single +5V supply option.                                                                                                         | 90 Pin Plug-In*<br>2.4" x 1.6"             | +5V                 | 1-47 |

<sup>\*</sup> Available in Flat Pack for Surface Mounting.

† Options deleting +15V(+12V) rail requirement to be introduced shortly.

# **Product List - Transceivers**

| Type No. | Description                                         | Package                              | Voltage   | Page |

|----------|-----------------------------------------------------|--------------------------------------|-----------|------|

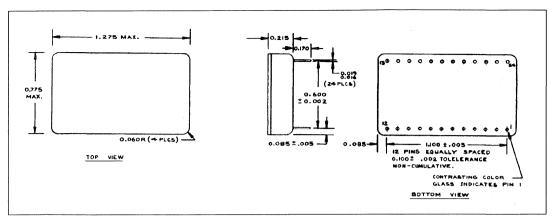

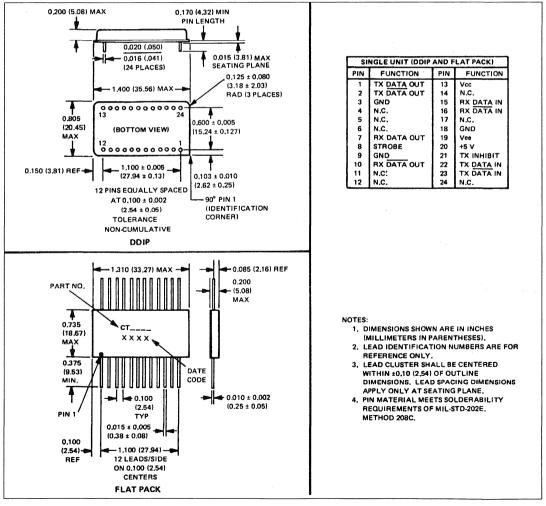

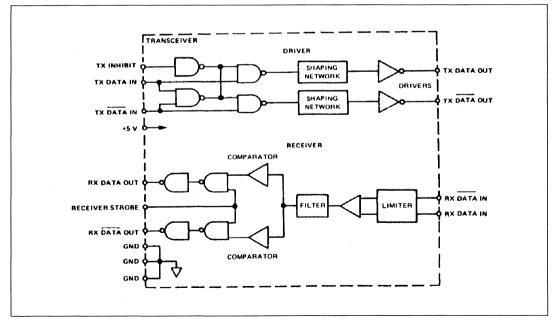

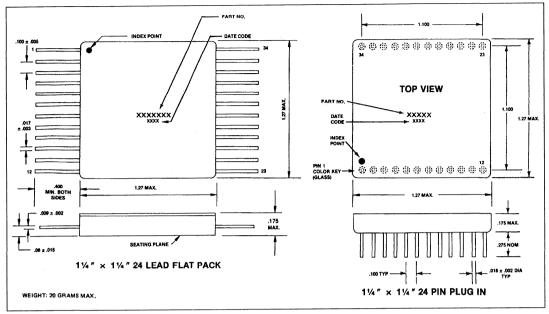

| CT1487M  | MIL-STD-1553A/B Single Transceiver.                 | 24 Pin Plug-In*<br>1.4" x 0.81"      | +5V, ±15V | 2-3  |

| CT1487MI | As CT1487M but with inverted receiver data outputs. | 24 Pin Plug-In*<br>1.4" x 0.81"      | +5V, ±15V | 2-3  |

| CT1487MP | MIL-STD-1553A/B Single Transceiver.                 | 24 Pin Plug-In<br>1.28" x 0.78"      | +5V, ±15V | 2-3  |

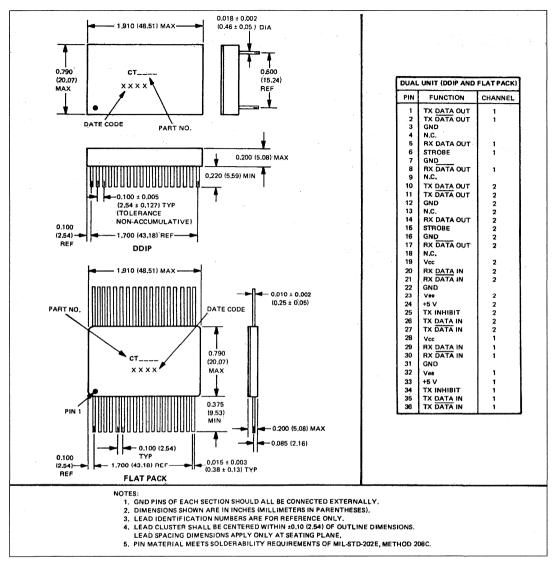

| CT1487D  | MIL-STD-1553A/B Dual Transceiver.                   | 36 Pin Plug-In*<br>1.91" x 0.79"     | +5V, ±15V | 2-3  |

| CT1487DI | As CT1487D but with inverted receiver data outputs. | 36 Pin Plug-In*<br>1.91" x 0.79"     | +5V, ±15V | 2-3  |

| CT1589M  | ±12V version of CT1487M.                            | 24 Pin Plug-In*<br>1.4" x 0.81"      | +5V, ±12V | 2-3  |

| CT1589MI | As CT1589M but with inverted receiver data outputs. | 24 Pin Plug-In*<br>1.4" x 0.81"      | +5V, ±12V | 2-3  |

| CT1589MP | ±12V version of CT1487MP.                           | 24 Pin Plug-In<br>1.28" x 0.78"      | +5V, ±12V | 2-3  |

| CT1589D  | ±12V version of CT1487D.                            | 36 Pin Plug-In*<br>1.91" x 0.79"     | +5V, ±12V | 2-3  |

| CT1589DI | As CT1589D but with inverted receiver data outputs. | 36 Pin Plug-In*<br>1.91" x 0.79"     | +5V, ±12V | 2-3  |

| CT2520   | MIL-STD-1553A/B Dual Transceiver                    | 36 Pin Plug-In*<br>1.91" x 0.79"     | +5V       | 2-11 |

| CT2521   | MIL-STD-1553A/B Dual Transceiver                    | 36 Pin Plug-In*<br>1.91" x 0.79"     | +5V       | 2-11 |

| CT2522   | MIL-STD-1553A/B Single Transceiver                  | 24 Pin Plug-In*<br>1.4" x 0.81"      | +5V       | 2-11 |

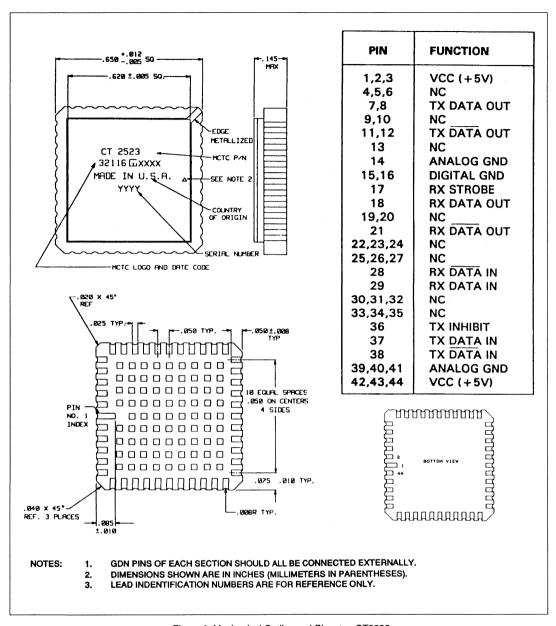

| CT2523   | MIL-STD-1553A/B Single Transceiver                  | 44 Pin Quad Plug-In<br>0.65" x 0.65" | +5V       | 2-11 |

<sup>\*</sup> Available in Flat Pack for Surface Mounting.

# **Product List - Transceivers (continued)**

| Type No. | Description                                       | Package                          | Voltage             | Page |

|----------|---------------------------------------------------|----------------------------------|---------------------|------|

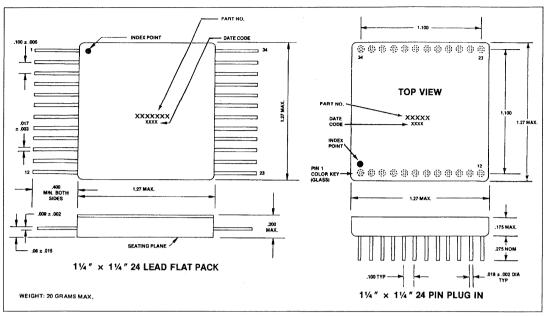

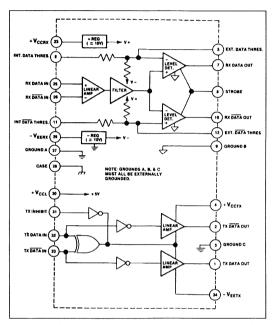

| CT3231M  | MIL-STD-1553A/B Single Transceiver                | 24 Pin Plug-ln*<br>1.27" x 1.27" | +5V, ±15V<br>±12V   | 2-19 |

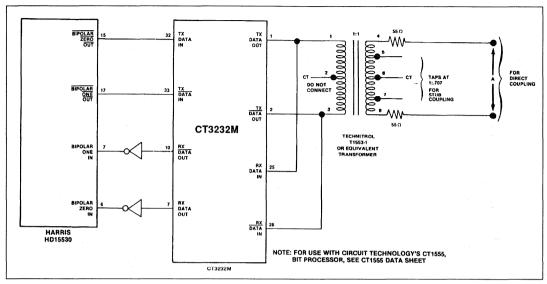

| CT3232M  | MIL-STD-1553A/B and MAC Air Single<br>Transceiver | 24 Pin Plug-ln*<br>1.27" x 1.27" | +5V,±15V<br>±12V    | 2-25 |

| MMT30000 | Compact MIL-STD-1553A/B Tx/Rx                     | 18 Pin Plug-In<br>0.98" x 0.78"  | +5V, ±15V           | -    |

| CT1816   | H009 Bus Transceiver                              | 24 Pin Plug-In<br>1.25" x 1.25"  | +5V,<br>±12V - ±15V | -    |

<sup>\*</sup> Available in Flat Pack for Surface Mounting.

# Product List - Transceiver/Protocol

| Type No. | Description                                                                                          | Package                         | Voltage                         | Page |

|----------|------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------|

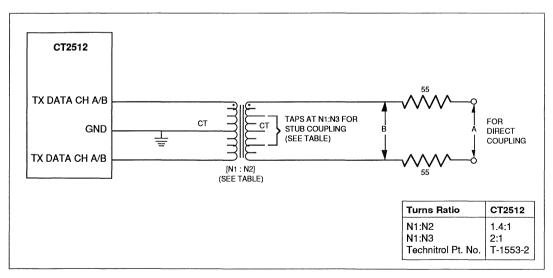

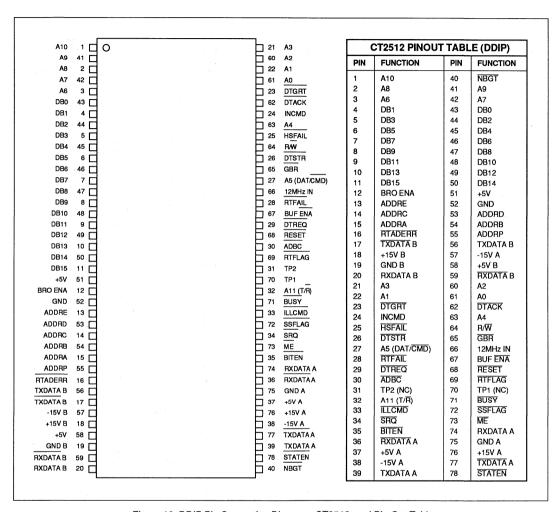

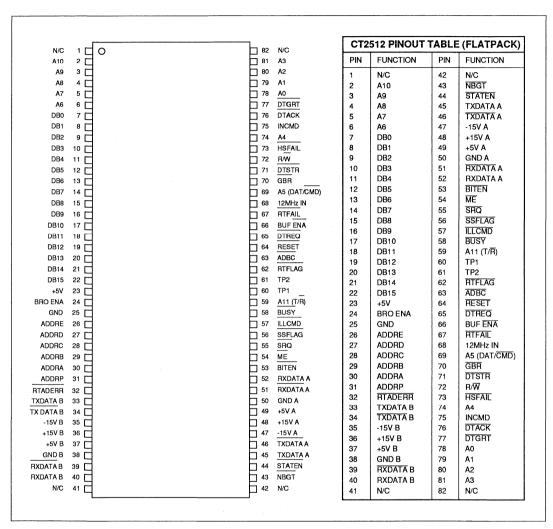

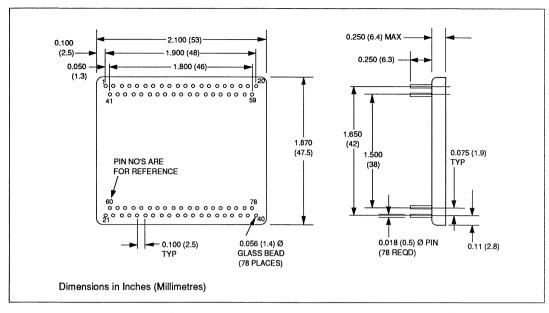

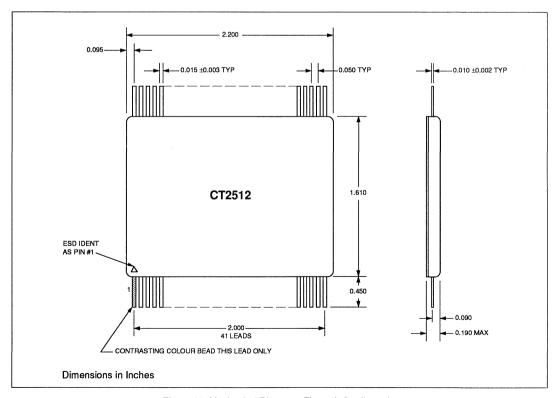

| CT2512   | R.T. MIL-STD-1553B Dual Transceiver.<br>Pin configurable to BUS65112/142.                            | 78 Pin Plug-In*<br>2.1" x 1.87" | +5V, ±15V                       | 3-3  |

| CT2513   | R.T. MIL-STD-1553B Dual Transceiver.<br>Pin configurable to BUS64113.                                | 78 Pin Plug-In*<br>2.1" x 1.87" | +5V, ±12V                       | 3-3  |

| CT1775   | MIL-STD-1553A/B Transceiver/Encoder.<br>S/P, P/S Connection.<br>Pin configurable to BUS65101 & 65102 | 76 Pin Plug-In<br>1.86" x 1.60" | +5V,<br>+12V - +15V,<br>-12V15V |      |

<sup>\*</sup> Available in Flat Pack for Surface Mounting.

# **Product List - Protocol**

| Type No.   | Description                                                                                | Package                                                               | Voltage | Page             |

|------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------|------------------|

| CT1602     | MIL-STD-1553B B.C./R.T./P.M.                                                               | 90 Pin Plug-In*<br>2.4" x 1.6"                                        | +5V     | 4-3              |

| CT1610     | MIL-STD-1553B B.C./R.T./P.M.                                                               | 90 Pin Plug-In*<br>2.4" x 1.6"                                        | +5V     | 4-3              |

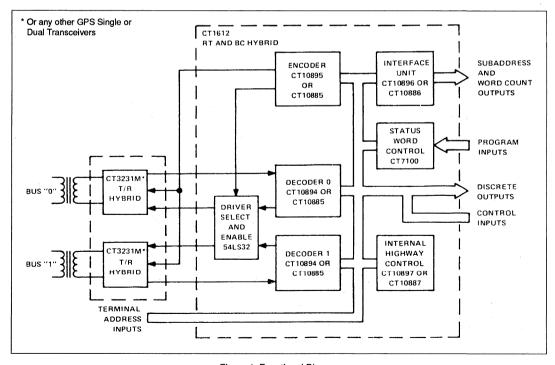

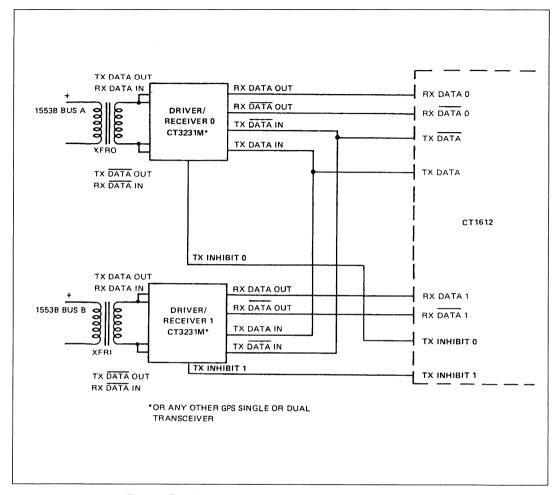

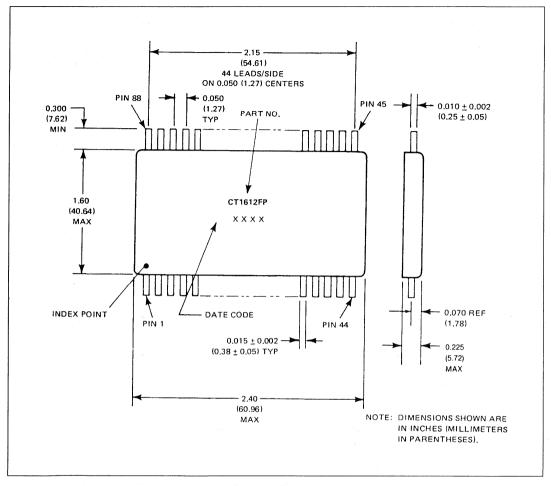

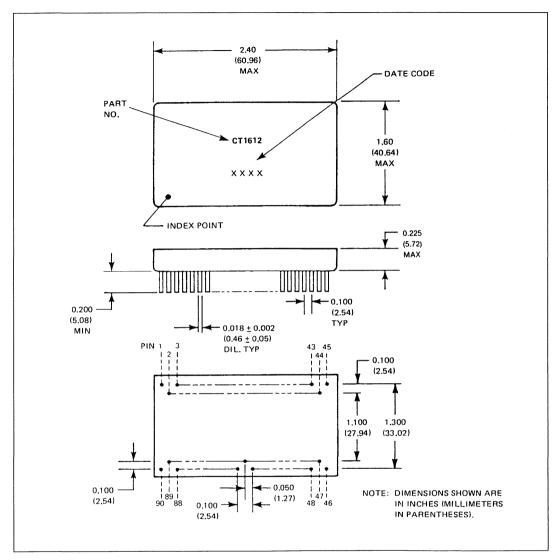

| CT1612     | MIL-STD-1553B B.C./R.T./P.M.                                                               | 90 Pin Plug-In*<br>2.4" x 1.6"                                        | +5V     | 4-29             |

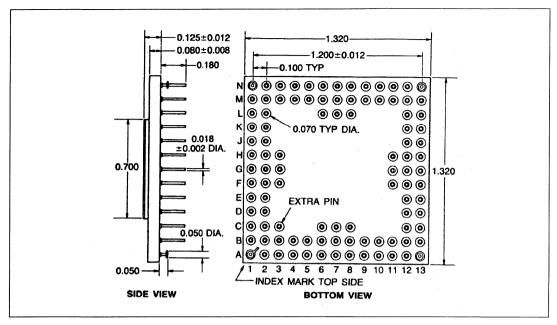

| CT1990     | MIL-STD-1553B B.C./R.T./P.M.                                                               | 90 Pin Plug-In*<br>2.4" x 1.6"<br>121 Pin Grid Array<br>1.32" x 1.32" | +5V     | 4-55             |

| CT1991     | MIL-STD-1553B B.C./R.T./P.M. With comprehensive self-test.                                 | 90 Pin Plug-In*<br>2.4" x 1.6"<br>121 Pin Grid Array<br>1.32" x 1.32" | +5V     | <del>-</del>     |

| CT2565     | MIL-STD-1553B B.C./R.T./P.M.                                                               | 78 Pin Plug-In*<br>2.1" x 1.87"                                       | +5V     | 4-57             |

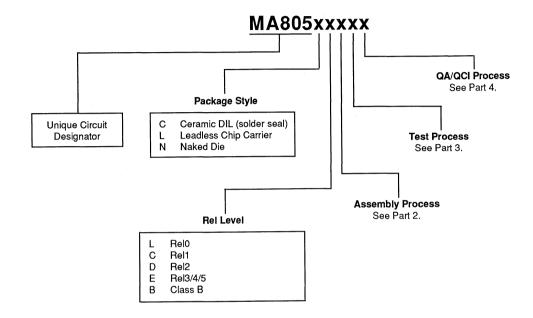

| MA805      | MIL-STD-1553B R.T./P.M.                                                                    | 40 Pin Plug-In<br>2.1" x 0.63"<br>40 Pin LCC<br>0.5" x 0.5"           | +5V     | 4-87             |

| MRTU53050  | MIL-STD-1553B R.T. for full protocol handling at message level.                            | Plug-In<br>2.65" x 1.6"                                               | +5V     | See<br>CT1602/10 |

| MRTU53050S | Single Channel version of MRTU53050.                                                       | Plug-In<br>2.65" x 1.6"                                               | +5V     | See<br>CT1602/10 |

| MRTU53053  | B.C./R.T./P.M. with Status bit control and Command illegalisation.                         | Plug-In<br>2.65" x 1.6"                                               | +5V     | See<br>CT1612    |

| MRTU53055  | MIL-STD-1553B B.C./R.T./P.M.                                                               | Plug-ln<br>2.65" x 1.6"                                               | +5V     | See<br>CT1602/10 |

| MRTU53055S | Single Channel version of MRTU53055.                                                       | Plug-ln<br>2.65" x 1.6"                                               | +5V     | See<br>CT1602/10 |

| MRTU53042  | MIL-STD-1553B B.C./R.T./P.M. with extended timeout option. Eg. For extra long buy lengths. | Plug-In<br>3.2" x 1.6"                                                | +5V     | -                |

<sup>\*</sup> Available in Flat-Pack for Surface Mounting.

# **Product List - Sub-System Interfaces**

| Type No. | Description                                                              | Package                                                            | Voltage | Page         |

|----------|--------------------------------------------------------------------------|--------------------------------------------------------------------|---------|--------------|

| CT2566   | MIL-STD-1553B to Microprocessor Interface<br>Pin compatible to BUS66300. | 78 Pin Plug-In*<br>2.1" x 1.87"<br>Pin Grid Array<br>1.32" x 1.32" | +5V     | 5-3          |

| CT1800   | MIL-STD-1553B to Microprocessor Interface.                               | 90 Pin Plug-In*<br>2.4" x 1.6"                                     | +5V     | 1 <b>2</b> 1 |

| CT1801   | As CT1800 except does not contain 2k x 16 message RAM internally.        | 90 Pin Plug-In*<br>2.4" x 1.6"                                     | +5V     | -            |

| CT1611   | MIL-STD-1553B to Microprocessor Interface.                               | 90 Pin Plug-In*<br>2.4" x 1.6"                                     | +5V     | e estate     |

<sup>\*</sup> Available in Flat-Pack for Surface Mounting.

# Product List - Encoder/Decoders

| Type No. | Description                                                                                          | Package                          | Voltage | Page |

|----------|------------------------------------------------------------------------------------------------------|----------------------------------|---------|------|

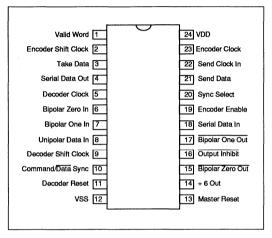

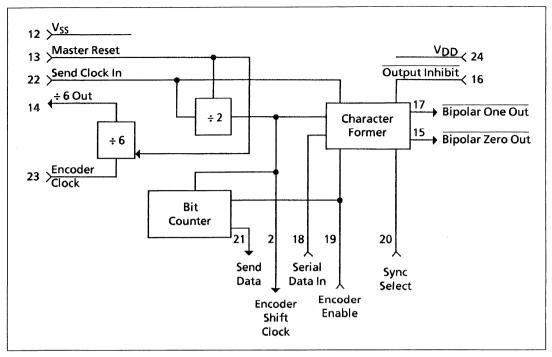

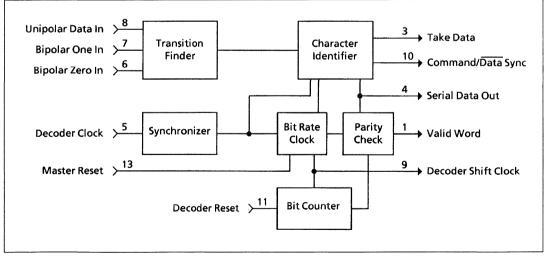

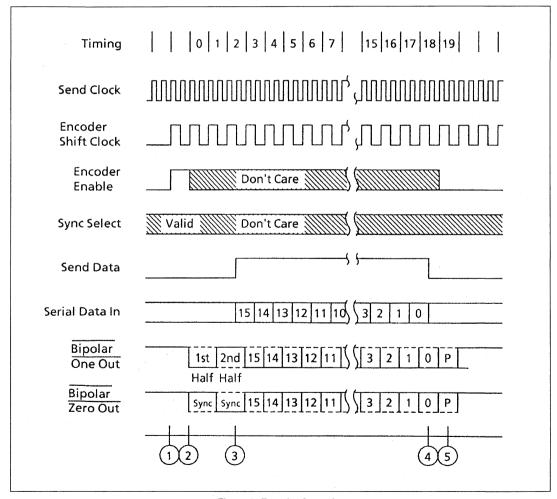

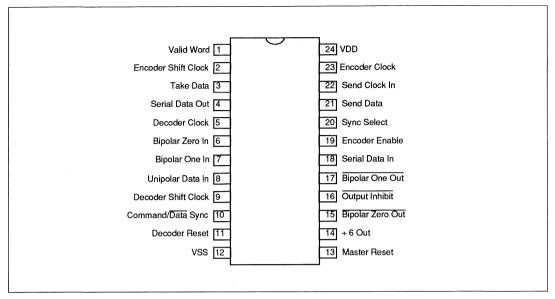

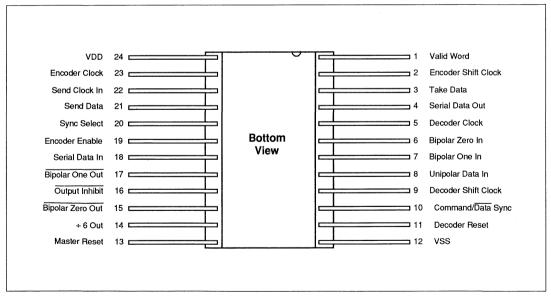

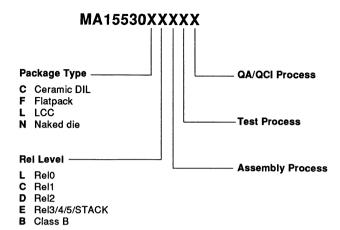

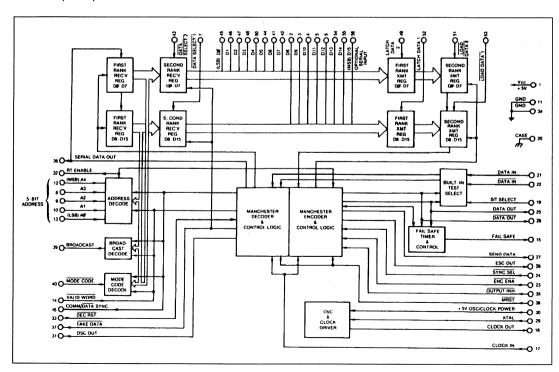

| MA15530  | MIL-STD-1553A/B and MAC Air B.C./R.T.<br>Manchester Encoder/Decoder.<br>Pin compatible with HD15530. | 24 Pin Plug-In<br>1.21" x 0.63"  | +5V     | 6-3  |

| CT1555-3 | MIL-STD-1553A/B and MAC Air B.C./R.T.                                                                | 56 Pin Plug-In*<br>2.16" x 1.16" | +5V     | 6-19 |

| CT1820   | MIL-STD-1553A/B and MAC Air B.C./R.T.                                                                | 56 Pin Plug-In*<br>2.16" x 1.16" | +5V     | 6-19 |

| CT1820-2 | As CT1820 except has internal buffers on the data lines.                                             | 56 Pin Plug-In*<br>2.16" x 1.16" | +5V     | 6-19 |

<sup>\*</sup> Available in Flat-Pack for Surface Mounting.

## **Product List - Cards**

| Type No. | Description                                            | Package | Voltage   | Page |

|----------|--------------------------------------------------------|---------|-----------|------|

| CT2600   | MIL-STD-1553/1773 to PC Card.                          |         |           | 7-3  |

| CT2605   | MIL-STD-1553 to MIL-STD-1773 Fibre Optic Gateway Card. |         | +5V, ±12V | 7-21 |

# Product List - Mil-Std-1397

| Type No. | Description                                                            | Package                                           | Voltage | Page |

|----------|------------------------------------------------------------------------|---------------------------------------------------|---------|------|

| CT1698   | MIL-STD-1397 Type 'E' Tx/Rx.<br>With internal transformer.             | 34 Pin Plug-In*<br>1.81" x 1.41"                  | ±5V     | 8-3  |

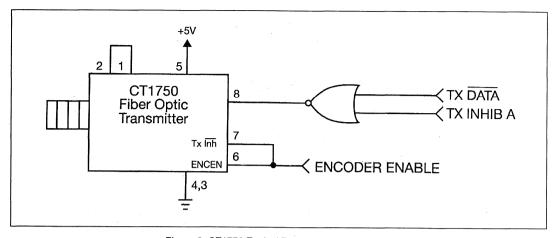

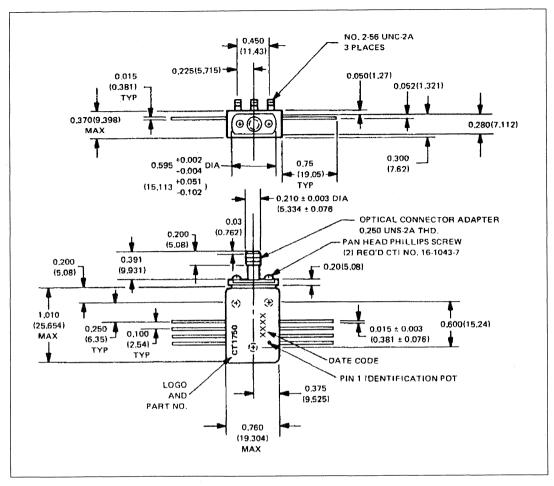

| CT1750   | 1/10MHz MIL-STD-1397 'J' or<br>MIL-STD-1773 Transmitter - Fibre Optic. | 8 Pin                                             | +5V     | 8-11 |

| CT1760   | 10MHz MIL-STD-1397 'J' Receiver - Fibre Optic.                         | 12 Pin                                            | ±5V     | 8-15 |

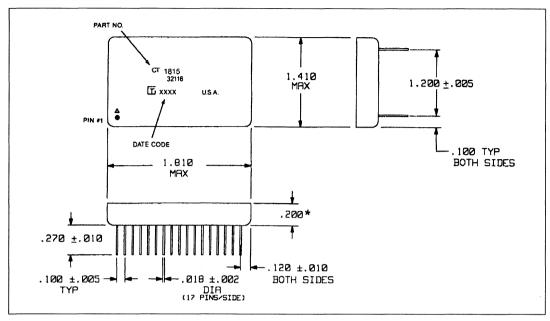

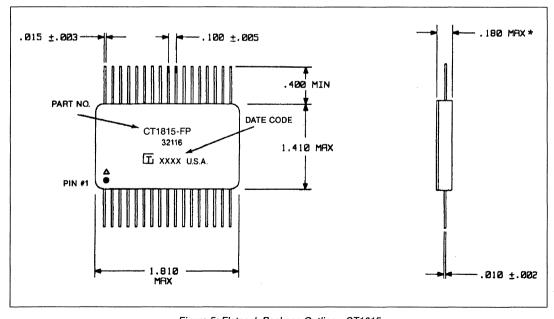

| CT1815   | 10MHz MIL-STD-1397 Type 'D' Low Level<br>Serial Interface.             | 34 Pin Plug-ln*<br>1.81" x 1.41"                  | ±5V     | 8-19 |

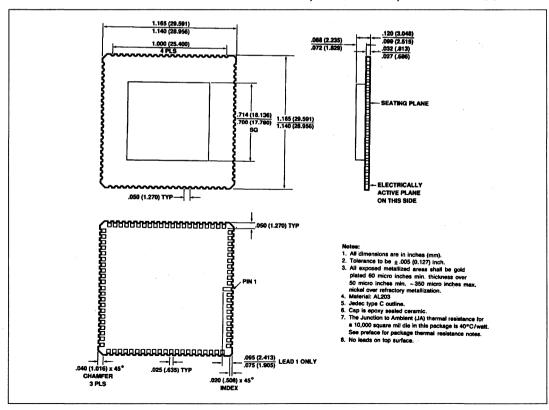

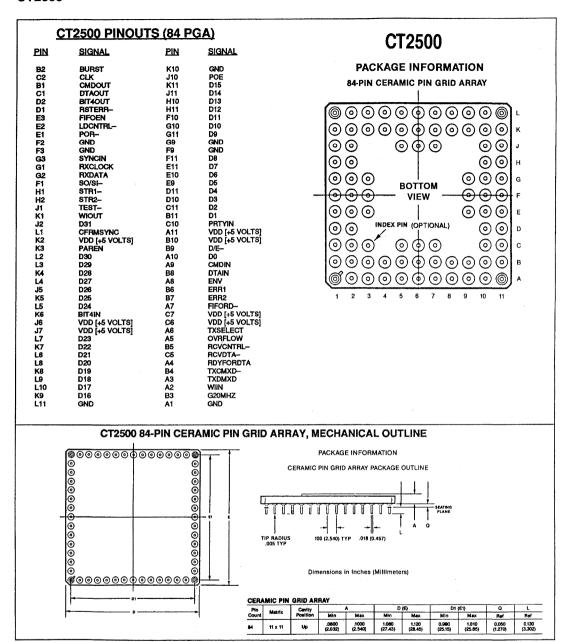

| CT2500   | MIL-STD-1397 Type 'E' Protocol.                                        | 84 Pin Ceramic<br>Pin Grid Array<br>1.12" x 1.12" |         | 8-27 |

| CT2500-1 | As CT2500.                                                             | 84 Pin LLCCC<br>1.17" x 1.17"                     |         | 8-27 |

| CT2505   | 10MHz MIL-STD-1397 Type 'E' Low Level<br>Serial Interface.             | 30 Pin Flat-Pack<br>1.56" x 1.36"                 | +5V     | -    |

<sup>\*</sup> Available in Flat-Pack for Surface Mounting.

# Product List - Mil-Std-1773 Fibre Optic

| Type No. | Description                               | Package | Voltage | Page |

|----------|-------------------------------------------|---------|---------|------|

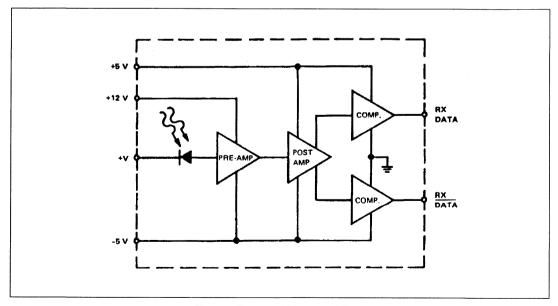

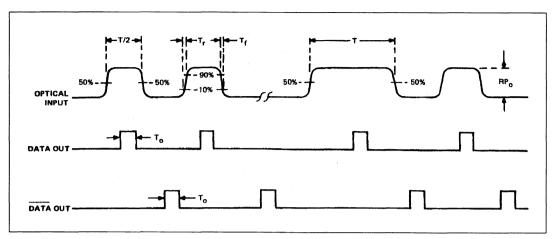

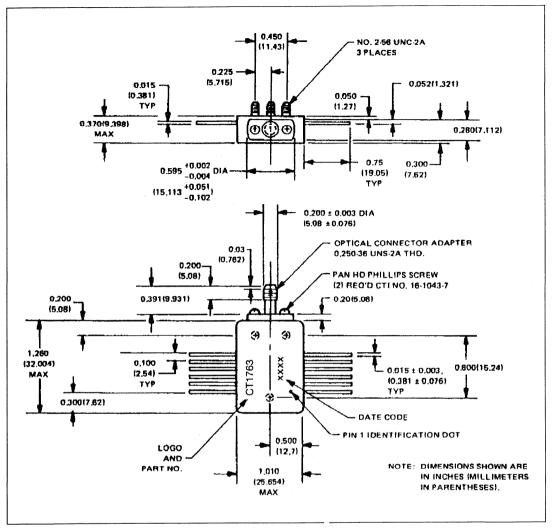

| CT1763   | 1MHz MIL-STD-1773 Receiver - Fibre Optic. | 12 Pin  | +5V     | 9-3  |

# Section 1 Complete Terminals

3032-1.4 November 1991

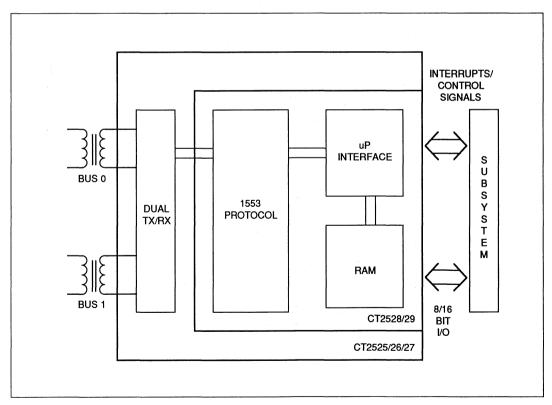

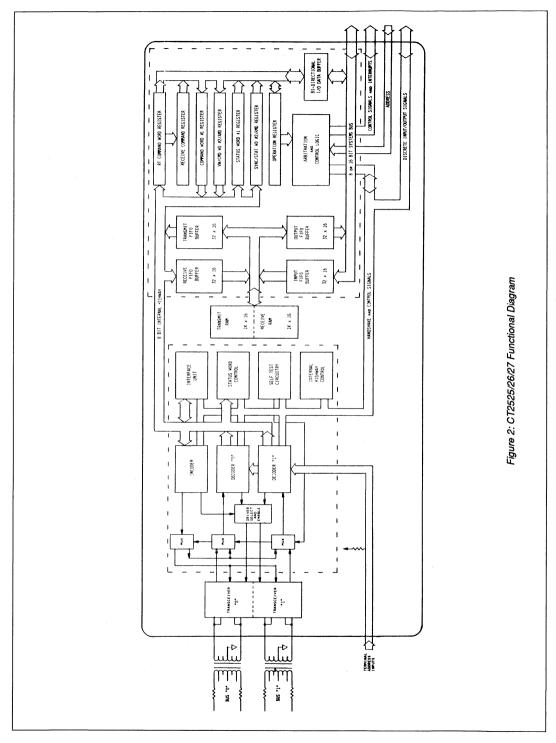

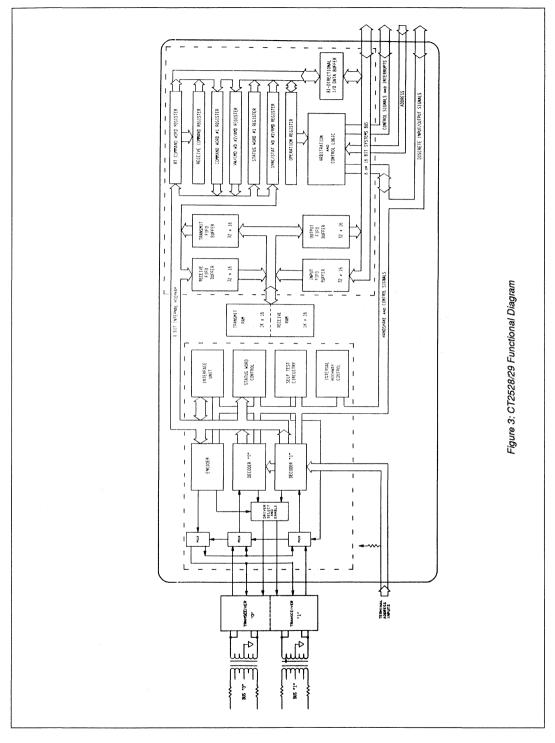

### **CT2525-29 Series**

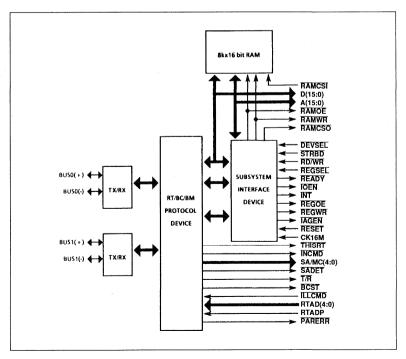

# SINGLE PACKAGE SOLUTION, DUAL TRANSCEIVER, PROTOCOL, SUBSYSTEM

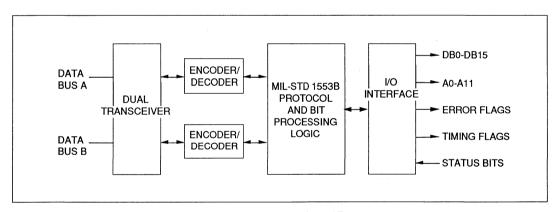

The CT2525 Series provides a complete one package interface between the MIL-STD-1553 bus and all microprocessor systems. The hybrid provides all data buffers and control registers to function as a Bus Controller or Remote Terminal. Control of the hybrid by the subsystem is through simple I/0 port commands. Internal hybrid logic removes all critical timing imposed on a typical subsystem, thereby simplifying the implementation of this interface.

#### **FEATURES**

- Incorporates Transceivers, Protocol, and System Interface components into a single Hybrid package

- Functions as a Remote Terminal or Bus Controller

- Interfaces to uP as a simple peripheral unit

- Available with several options for transceivers: ±15V, ±12V, and ±5V

- Provides 2k by 16 of Double Buffered RAM storage for transmit and receive subaddresses

- Pin programmable for 8-bit or 16-bit microprocessors

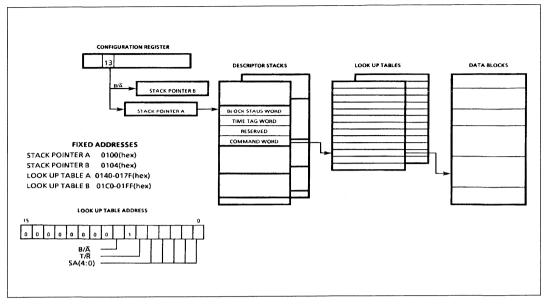

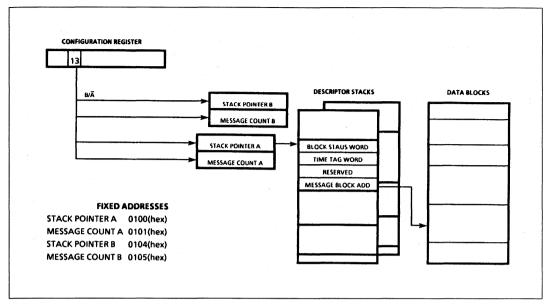

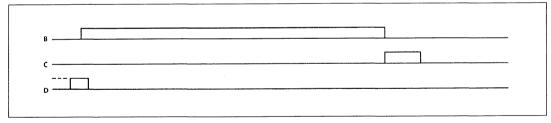

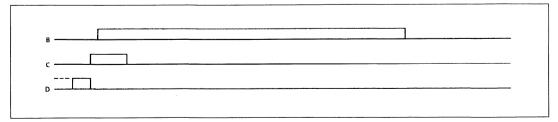

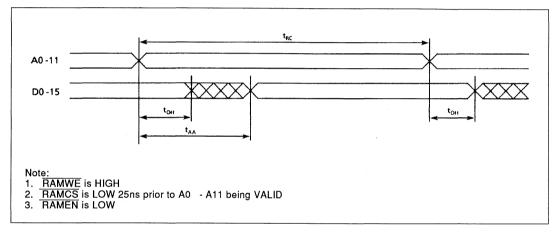

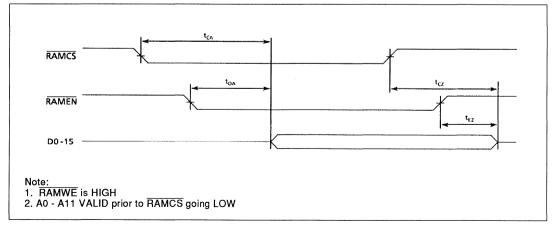

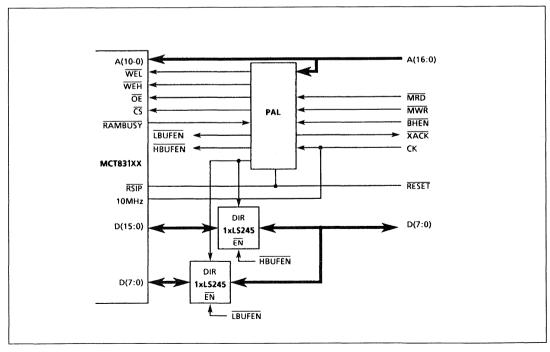

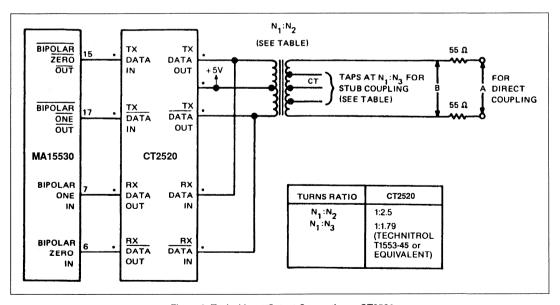

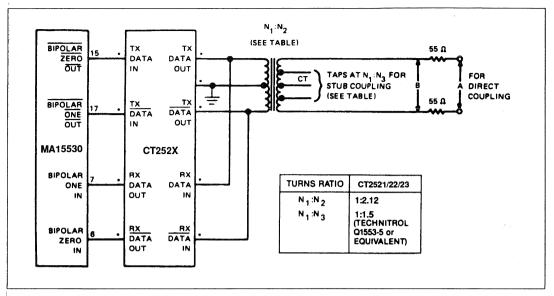

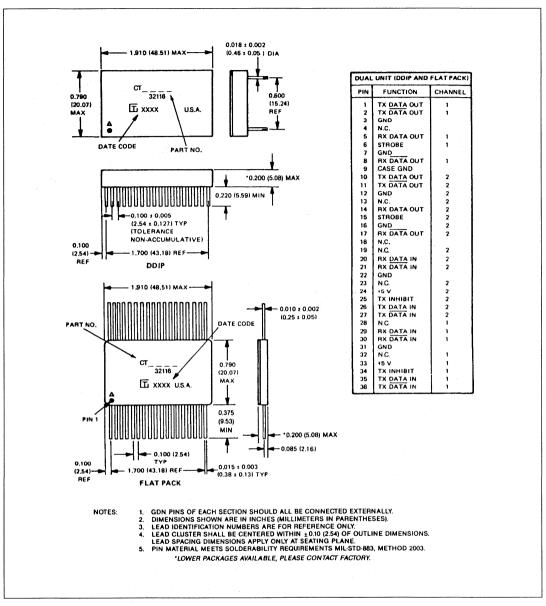

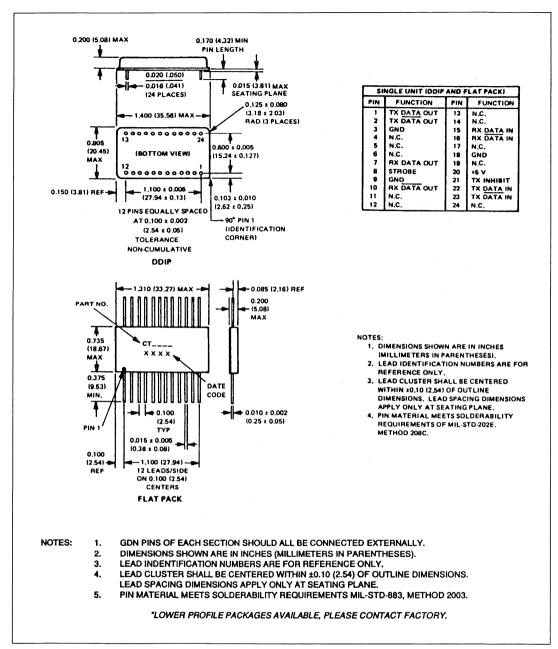

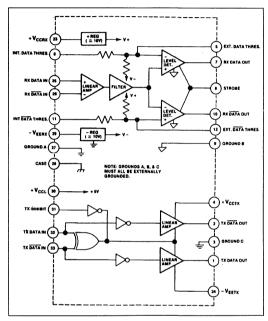

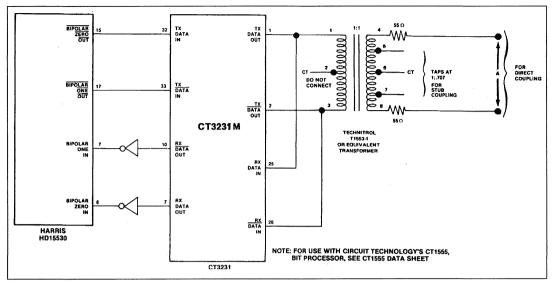

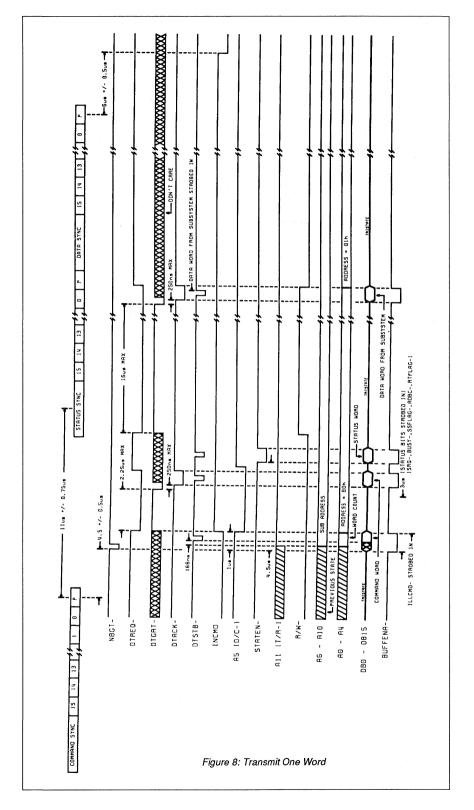

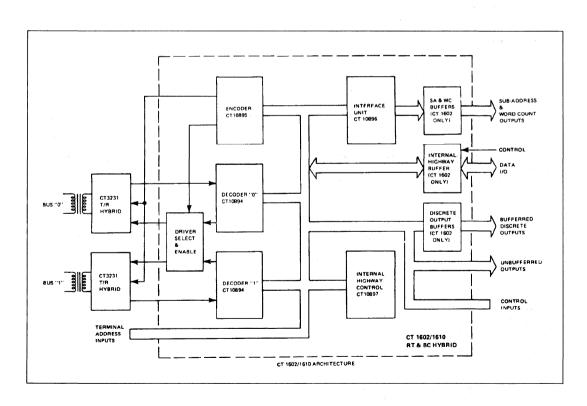

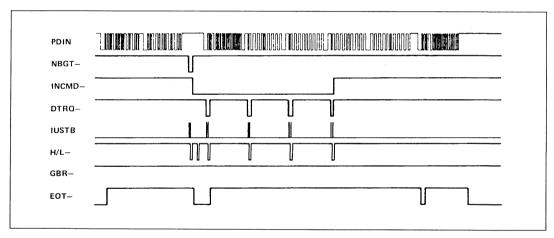

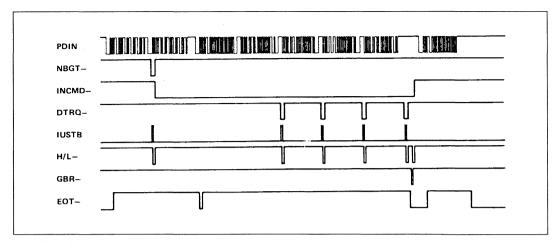

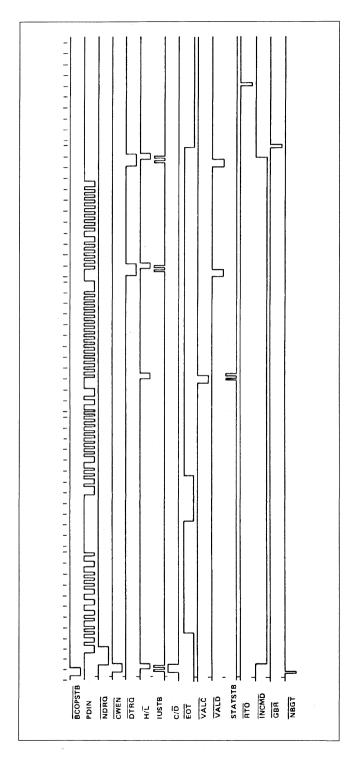

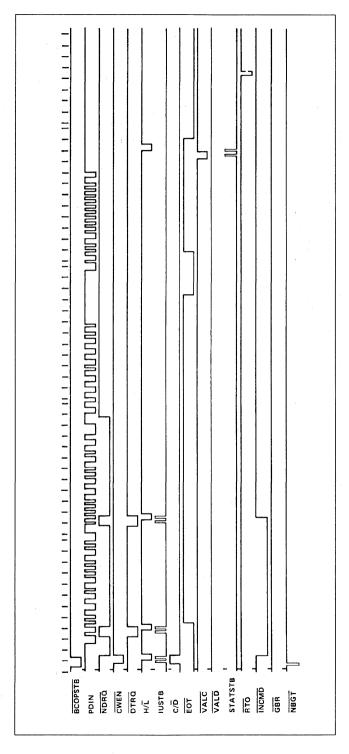

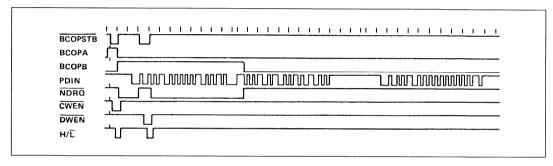

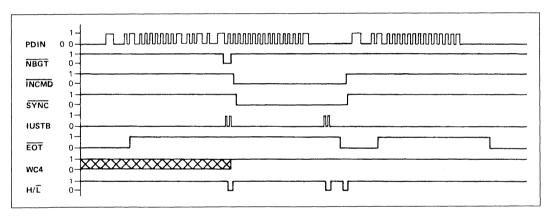

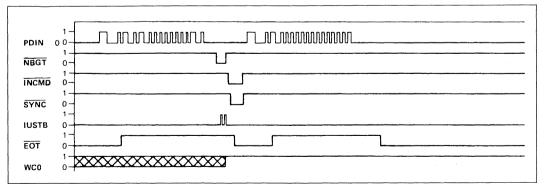

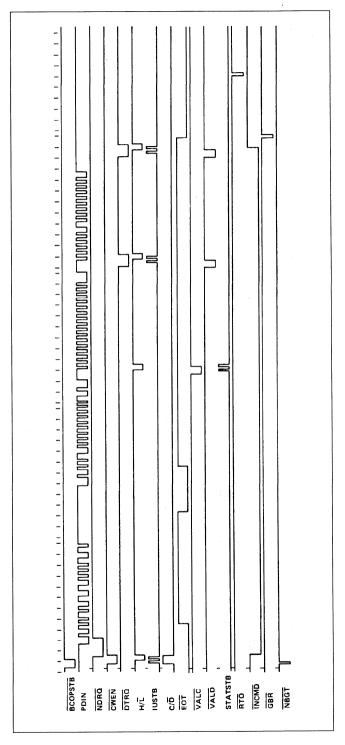

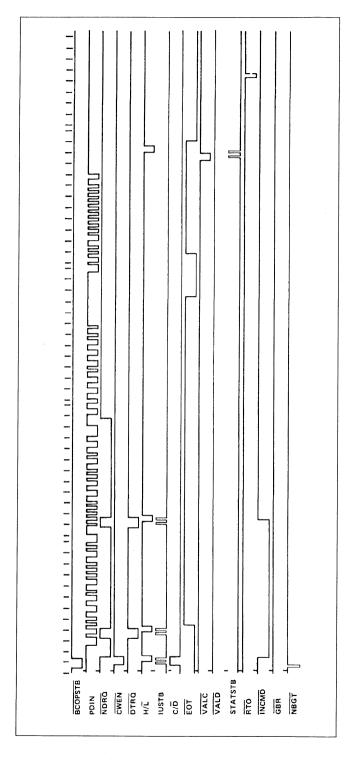

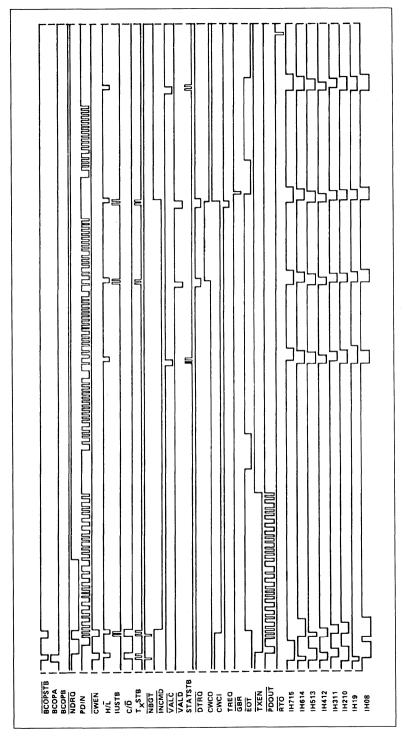

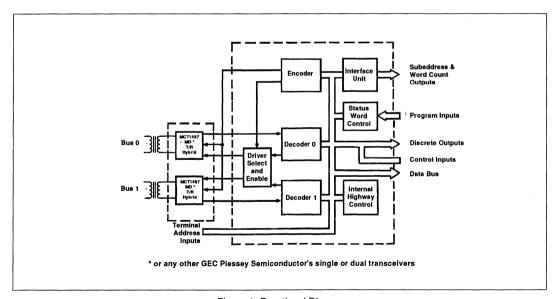

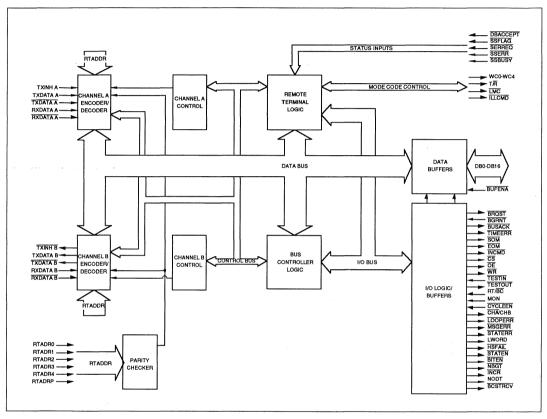

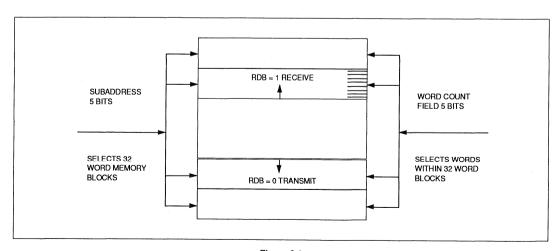

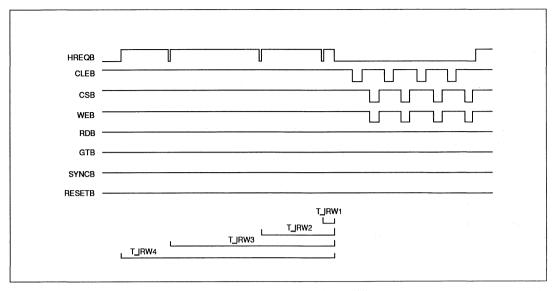

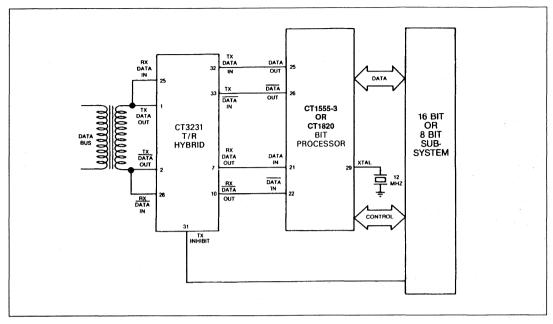

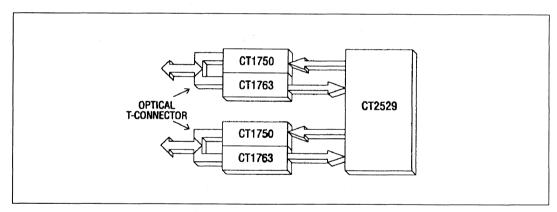

Figure 1: CT252X Block Diagram

| ABSOLUTE MAXIMUM RATINGS                                    | DEVICE                                         | LIMITS                                                       |

|-------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|

| Power Supply Voltage (Vcc)                                  | CT2525<br>CT2526<br>CT2527<br>CT2528<br>CT2529 | -0.3V to +18V<br>-0.3V to +18V<br>-0.3V to +7V<br>N/A<br>N/A |

| Power Supply Voltage (Vee)                                  | CT2525<br>CT2526<br>CT2527<br>CT2528<br>CT2529 | -0.3V to +18V<br>-0.3V to +18V<br>N/A<br>N/A<br>N/A          |

| Power Supply Voltage<br>(VccL and VDD)                      | ALL                                            | -0.3V to +7V                                                 |

| Receiver Differential Input<br>(DATA CH A/B / DATA- CH A/B) | CT2528<br>CT2529                               | ±20V (40V p-p)<br>Subject to Ext<br>Transceiver Used         |

| Receiver Input Voltage<br>(DATA CH A/B or DATA- CH A/B)     | CT2528<br>CT2529                               | ±15V<br>Subject to Ext<br>Transceiver Used                   |

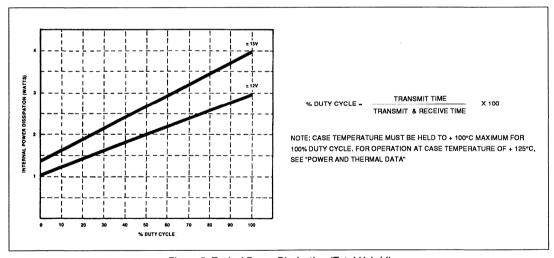

| Transmission Duty Cycle at Tc=125°C                         | CT2528<br>CT2529                               | 100%<br>Subject to Ext<br>Transceiver Used                   |

| Operating Case Temperature Range (Tc)                       | ALL                                            | -55 to +125°C                                                |

Table 1: CT2525/26/27/28/29 Characterisics

| PARAMETER/CONDITION                                                                                                                                 | SYMBOL                                                         | MIN                                  | ТҮР                    | MAX                      | UNITS          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------|------------------------|--------------------------|----------------|

| CT2525 Power Supply Voltages                                                                                                                        | Vcc<br>Vee<br>VccL                                             | 14.25<br>-14.25<br>4.5               | 15<br>-15<br>5         | 14.75<br>-15.7<br>5.5    | V<br>V         |

| CT2526 Power Supply Voltages                                                                                                                        | Vcc<br>Vee<br>VccL                                             | 11.4<br>-11.4<br>4.5                 | 12<br>-12<br>5         | 12.6<br>-12.6<br>5.5     | V<br>V<br>V    |

| CT2527 Power Supply Voltages                                                                                                                        | Vcc                                                            | 4.5                                  | 5                      | 5.5                      | ٧              |

| Total supply current 'standby'<br>mode or transmitting at less<br>than 1% duty cycle (e.g. 20us of<br>transmission every 2ms or<br>longer interval) | CT2525/26<br>lcc<br>lee<br>lccL<br>CT2527<br>lcc               | Note 1<br>Note 1                     | 30<br>50<br>64         | 50<br>70<br>90           | mA<br>mA<br>mA |

| Total supply current transmitting at 1MHz into a 35 ohm load at point A in Figure 1.                                                                | CT2525<br>lcc@25%<br>lcc@100%<br>CT2526<br>lcc@25%<br>lcc@100% | Note 2<br>Note 2<br>Note 2<br>Note 2 | 70<br>200<br>85<br>240 | 100<br>260<br>120<br>315 | mA<br>mA<br>mA |

|                                                                                                                                                     | lcc@25%<br>lcc@100%                                            | Note 2<br>Note 2                     | 225<br>535             | 270<br>610               | mA<br>mA       |

Note 1: lee and lccL limits do not change with mode of operation or duty cycle. Transceiver section only.

Note 2: Decreases linearly to applicable "standby" values at zero duty cycle.

Table 2: CT2525/26/27 Transceiver Characteristics Power Supply Data (Transceiver Section)

| PARAMETER/CONDITION                                                                                | SYMBOL       | MIN      | TYP | MAX | UNITS          |

|----------------------------------------------------------------------------------------------------|--------------|----------|-----|-----|----------------|

| Differential input impedance DC to 1MHz                                                            | Zin          | 9K       |     |     | ohms           |

| Differential voltage range                                                                         | Vdir         | ±20V     |     |     | Vpeak          |

| Input common mode voltage range                                                                    | Vicr         | ±10V     |     | -   | Vpeak          |

| Common mode rejection ratio (from point A, Figure 4)                                               | CMRR         | 40       |     |     | dB             |

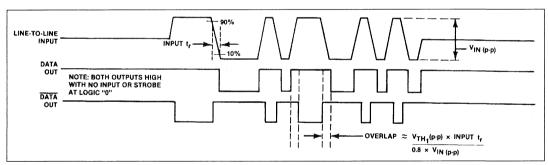

| Threshold characteristics (sine wave at 1MHz) NOTE: Threshold voltages refer to point A, Figure 4. | Vth1         | 0.8      |     | 1.1 | V p-p          |

| Filter Characteristics                                                                             | Vth2<br>Vth3 | 1.5<br>5 |     | 8   | V p-p<br>V p-p |

Table 3: CT2525/26/27 Transceiver Characteristics Electrical Characteristics (Receiver Section All Devices)

| PARAMETER/CONDITION                                                                                                           | SYMBOL                    | MIN | ТҮР | мах | UNITS   |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|-----|-----|---------|

| Differential output level at point B,<br>Figure 4 (145 ohm load)                                                              | CT2525/26<br>Vo<br>CT2527 | 26  | 28  | 35  | V p-p   |

|                                                                                                                               | Vo                        | 25  | 27  | 35  | V p-p   |

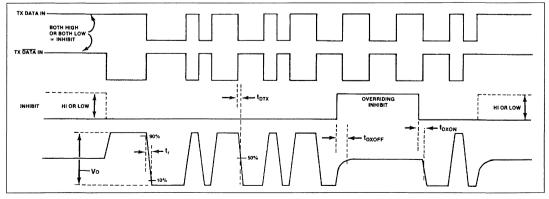

| Rise and Fall times (10% to 90% of p-p output)                                                                                | Tr                        | 100 | 160 | 300 | ns      |

| Output offset at point A in Figure 4 (35 ohm load) 2.5us after mid-bit crossing of parity bit of last word of a 660us message | Vos                       |     | ±20 | ±75 | mV peak |

| Differential output noise                                                                                                     | Vnoi                      |     |     | 10  | mV p-p  |

| Differential output impedance (inhibited) at 1MHz                                                                             | Zoi                       | 8K  |     |     | ohms    |

Table 4: CT2525/26/27 Transceiver Characteristics Electrical Characteristics (Transmitter Section All Devices except as noted)

| Symbol            | Parameter    | Min  | Тур | Max  | Units | Conditions |

|-------------------|--------------|------|-----|------|-------|------------|

| V <sub>DD</sub>   | Logic Supply | 4.5  | 5.0 | 5.5  | VDC   |            |

| V <sub>IH</sub>   | Input "1"    | 2.0  |     |      | VDC   |            |

| V <sub>IL</sub>   | Input "0"    |      |     | 0.8  | VDC   |            |

| I <sub>IL</sub> . | Input I      | -450 |     | -900 | uA    | Note 1A    |

| I <sub>IH</sub>   | Input I      | -600 |     |      | uA    | Note 1B    |

| I <sub>IL</sub>   | Input I      | -50  |     | -800 | uA    | Note 1C    |

| I <sub>IH</sub>   | Input I      | -500 |     |      | uA    | Note 1D    |

| I <sub>IL</sub>   | Input I      | -25  |     | -400 | uA    | Note 2A    |

| I <sub>IH</sub>   | Input I      | -250 |     | es e | uA    | Note 2B    |

| V <sub>OH</sub>   | Output "1"   | 2.4  |     |      | VDC   | Note 3A    |

| V <sub>OL</sub>   | Output "0"   |      |     | 0.4  | VDC   | Note 3B    |

| V <sub>DD</sub>   | Static I     |      | 40  |      | mA    | Note 4A    |

| V <sub>DD</sub>   | Dynamic I    |      |     | 170  | mA    | Note 4B    |

Conditions: Operating Temperature Range (T<sub>C</sub>) -55° to +125°C

Notes: 1.  $V_{DD} = 5.5V$

A. For RTAD0/1/2/3/4 and RTADPAR with  $V_{iL} = 0.4V$

B. For RTAD0/1/2/3/4 and RTADPAR with  $V_{\rm IH} = 2.4 V$

C. FOR BCSTEN WITH V<sub>IL</sub> = 0.4V

D. FOR BCSTEN WITH V<sub>IH</sub> = 2.4V

2. All remaining inputs and I/O

$$V_{DD} = 5.5V$$

A.

$$V_{IL} = 0.4V$$

B.

$$V_{IH} = 2.4V$$

3. A.

$$V_{DD}$$

= 4.5V and  $I_{OH}$  = 3mA

B.  $V_{DD}$  = 5.5V and  $I_{OL}$  = 3mA

A. Clock Input = 6MHz (40-60% Duty Cycle / TTL Levels)

All remaining Inputs = V<sub>DD</sub>

All Outputs = Open Circuit

B. During a 32 word FIFO to RAM or RAM to FIFO block Move.

Table 5: CT2525/26/27/28/29 Logic Characteristics

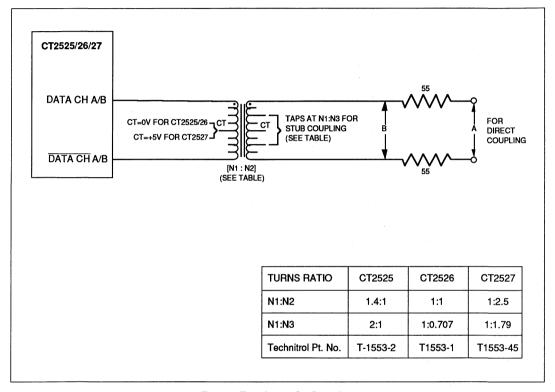

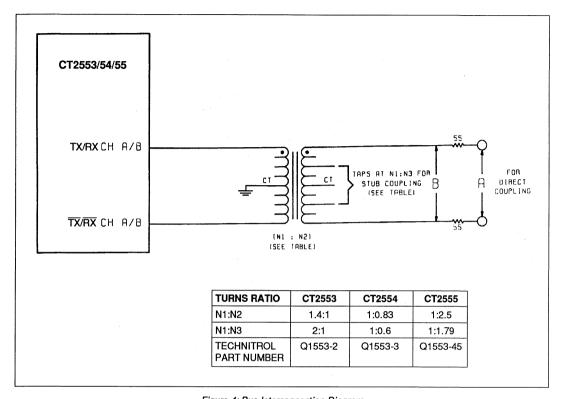

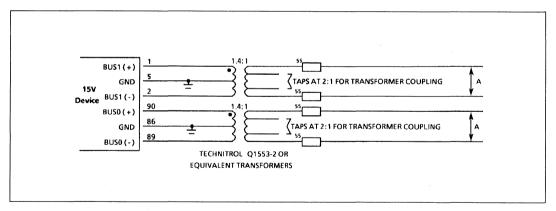

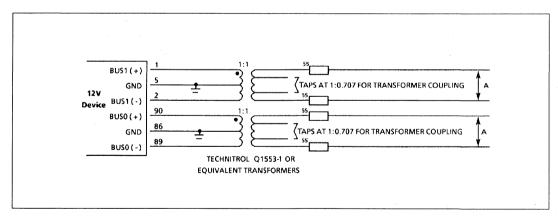

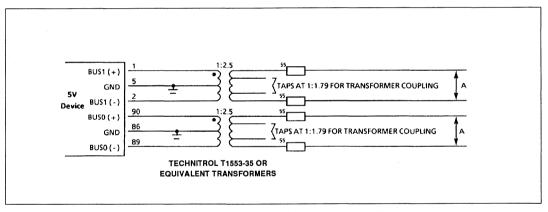

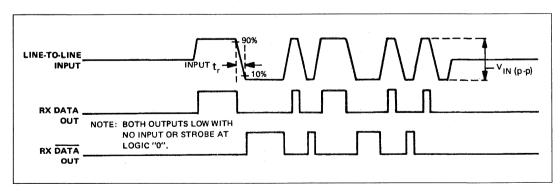

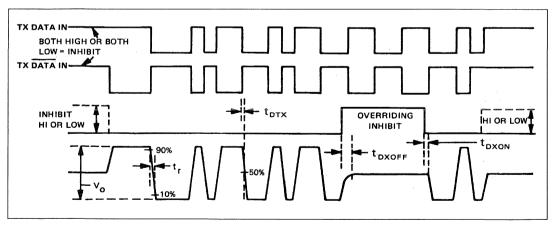

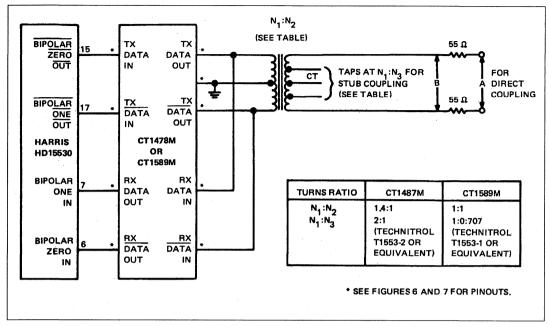

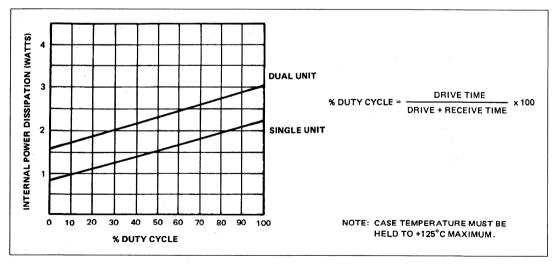

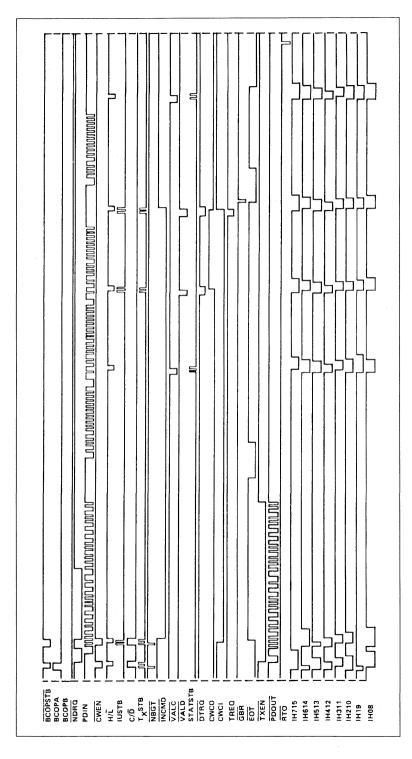

Figure 4: Transformer Configurations

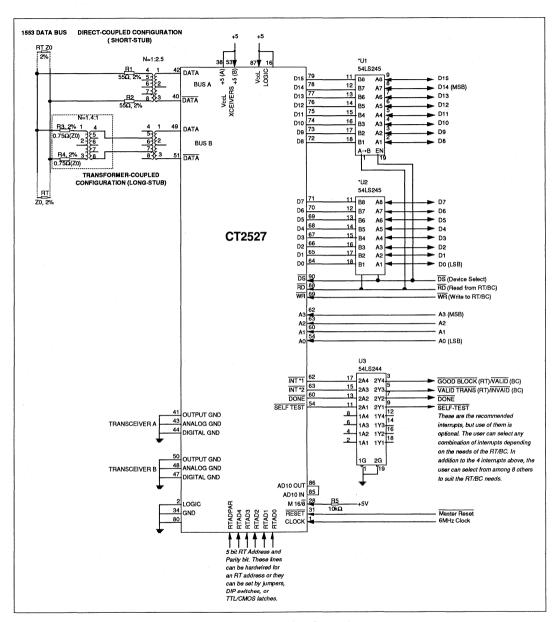

Figure 5: Typical Interface Connections

## SINGLE HYBRID PROTOCOL SUBSYSTEM INTERFACE

#### **Kev Features**

- Functional Superset of CT1800

- Downward compatible with existing designs base of CT1800

- Incorporates Transceivers, Protocol and Interface Hybrids into a single package

- Functions as a Remote Terminal or Bus Controller

#### General

The CT25XX Series provides a complete interface between the MIL-STD-1553 bus and any micro-processor system. Functioning as a superset of the CT1800 interface, the hybrid provides all data buffers and control registers necessary to implement RT and BC functions. Internal arbitration and data transfer control circuitry eliminates subsystem response requirements. All data written into or read from this interface are double buffered on a message basis. Only valid and complete receive messages are transferred into the receive RAM.

The CT25XX Series supports all 15 mode codes and all types of data transfers allowed by MIL-STD-1553B. All circuitry (excluding transceiver drivers) are CMOS, which results in very low power requirements.

Interfacing to the subsystem is simplified through the use of tri-stated input/output buffers onto the subsystem bus. Control signals basically consist of four address lines, a device select input, read strobe, write strobe, and several interrupts, the use of which are optional. The Hybrid is accessed as a memory mapped I/O port of a microprocessor system. Valid transmission and reception of data are indicated to the subsystem through the use of interrupts. This frees up the system processor from actively monitoring the port until a valid message is received.

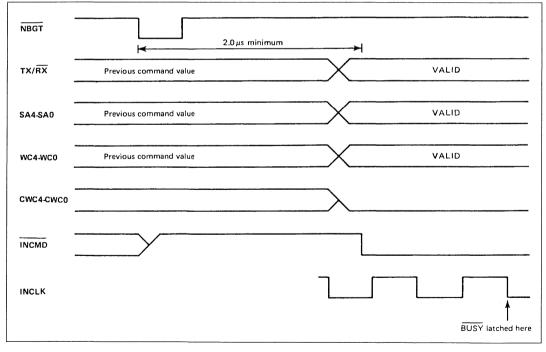

#### **OPERATION**

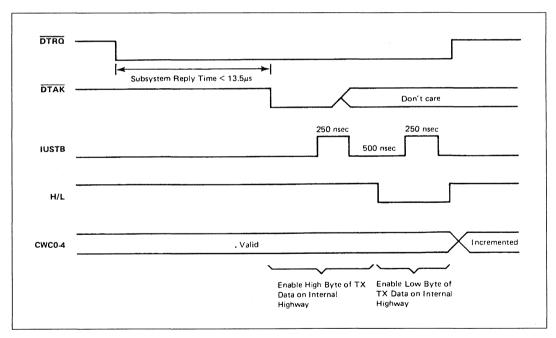

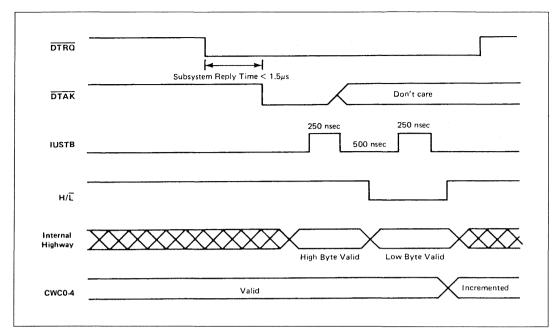

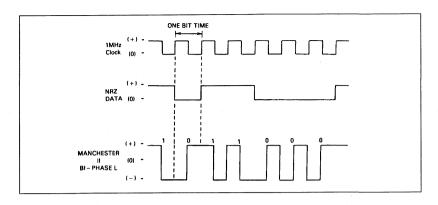

The CT25XX Series (Single Package Solution) resides between a microprocessor interface and a MIL-STD-1553 data bus. The addition of two transformers and fault isolation resistors are the only external components required to complete the interface. Information on the bus is received or transmitted through the transceiver (converted from Manchester II to complimentary TTL signals and visa versa) to the protocol section. The type transceiver employed determines the actual part number. The CT2525 Series incorporates a +5VDC and ±15VDC transceiver, while the CT2526 is a +5VDC and ±12VDC type. The CT2527 is a single +5VDC only transceiver, and the CT2528 contains no transceiver allowing external single or dual transceiver use.

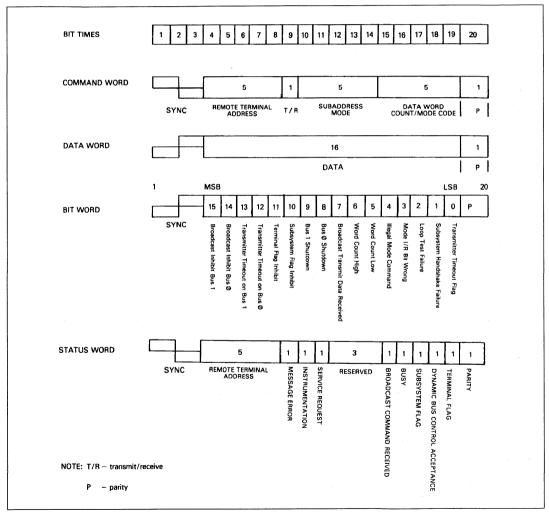

The protocol section internally interfaces to the transceivers. Control of the transceivers is provided by the protocol section. This is determined by which bus the command word was received on in the remote terminal mode; or in the bus controller mode, which bus was selected for transmission by the state of a bit in the operation register. The protocol section is very similar to our CT1600 series of protocol devices, with the exception that it is a single chip implementation with an extensive self-test function. An autonomous self-test can be performed either offline or on-line through the transceivers This self-test is controlled by the operation register and will be discussed thoroughly in the self-test section. The other test function is that in addition to the protocol criteria that is tested during every transmission; i.,e., proper sync character, 16 data bits. Manchester II coded. contiguous words, and odd parity, a bit per bit comparison of the contents of the parallel data will insure a higher degree of functionality of this section of the hybrid.

Data received by the protocol section will be placed in the receive FIFO buffer. Transmitted data will be taken from the transmit FIFO buffer. Other than the remote terminal address and parity, the discretes to control the resetting of the terminal flag and subsystem error bits, and a few discrete interrupts and error signals, control over the protocol section resides in the operation register of the subsystem interface section.

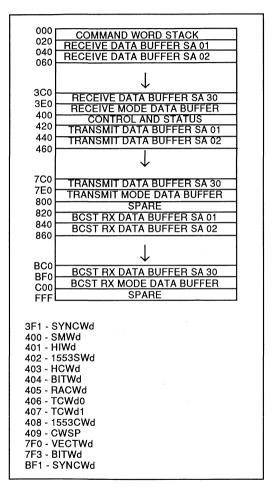

The subsystem interface section has primary control of the data that resides in the 2k of RAM. The RAM is segregated into two 1 k blocks of data, one contains 30 blocks of transmit data messages and the other one contains 30 blocks of receive data messages. This is not absolute since the subsystem has control of the A10 bit. Data entries to or from the RAM are arbitrated by the control logic residing in this function, and is buffered via FIFO's on the input from the protocol section and on the output to the subsystem's data bus. This guarantees that only current and valid data blocks will reside in RAM. This is true for remote terminal and bus controller applications.

Seven dedicated registers are provided to ease the interfacing with the subsystem. These will be discussed in the Register Operation section of this document. The register of primary concern to a subsystem designer is the operation register. This provides the means to accomplish data transfers to/from the RAM, as well as control of remote terminal or bus control modes of operation. All registers are accessed via simple I/O commands, utilizing A0 through A3, Device Select, and Read or Write strobes.

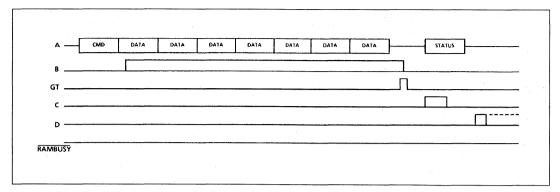

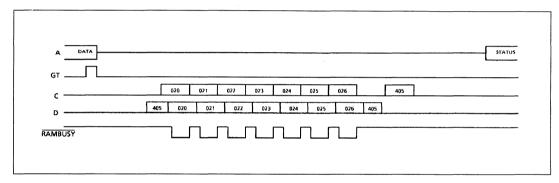

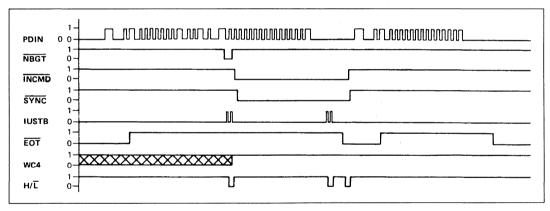

#### **Receive Commands**

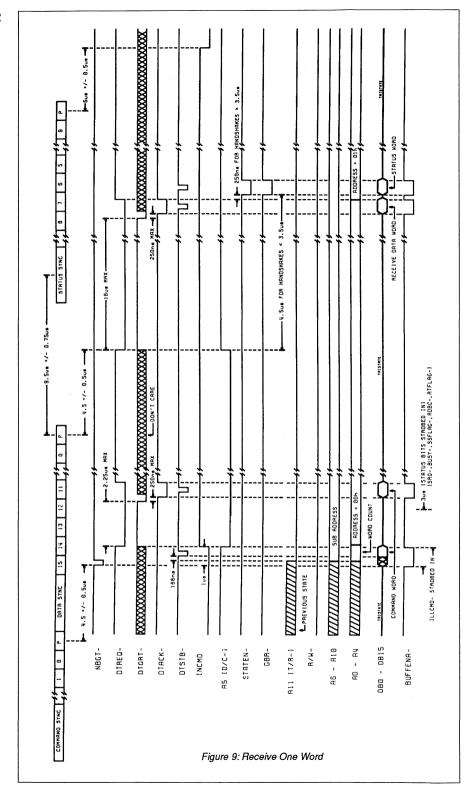

When a valid receive command is received, it is first loaded into the Command Word Register. The data words associated with this command are received, validated, and loaded one by one into the RCV FIFO buffer. Once the entire message is received, and only if the complete block of data is valid, will the command word be transferred to the RCV Command Register. This block of data is then burst (by the internal controller) into the corresponding internal RAM location, which is memory mapped by the subaddress contained in the RCV Command Register. Once this operation is complete, a discrete interrupt pulse called INT #1 is sent the subsystem.

If this interrupt is used, the subsystem would read the command word from the RCV Command Register. The data could then be transferred to the OUTPUT FIFO buffer, and read by the subsystem. Each receive subaddress section of the internal RAM will contain only the most recent, valid, and complete block of data to that subaddress. This is true for Remote Terminal and Bus Controller operations.

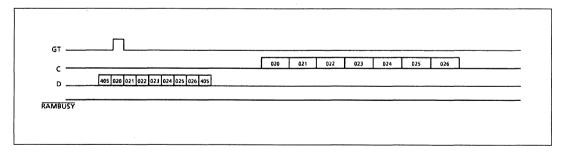

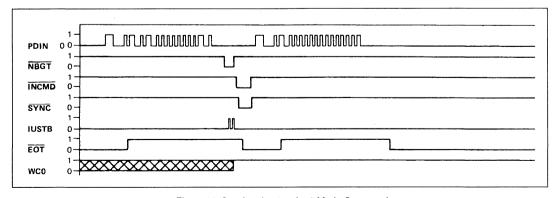

#### **Transmit Commands**

If a valid transmit command is received, the command word is first loaded into the Command Word Register. The block of data corresponding to the subaddress of the transmit command is then transferred from the internal RAM to the XMIT FIFO buffer. Upon completion of this transfer, INT #2 is sent to the subsystem.

The transmit section of the internal RAM is generally initialized at power up and periodically updated as required.

Appropriate subsystem response to INT #2 for an RT implementation would be to read the command word from the Command Word Register. The data to this subaddress could now be refreshed in preparation for the next time it was requested to be transmitted across the 1553 bus.

#### **Mode Codes**

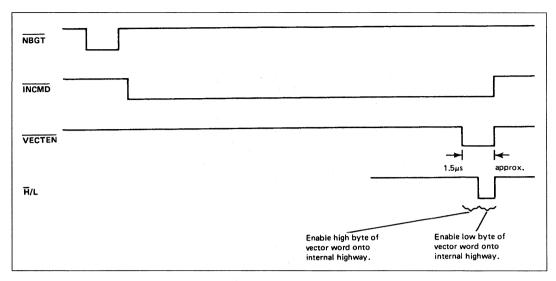

All 15 mode codes are serviced by the protocol section, and most do not require subsystem intervention. Discrete interrupt signals are available for each of the Synchronize (with and without data), Vector Word, Reset, and Dynamic Bus Control Acceptance mode codes. Mode command words are loaded into the Command Word Register. Separate registers are provided for the synchronize data word and the vector data words.

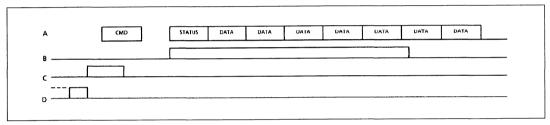

#### **Bus Control Operation**

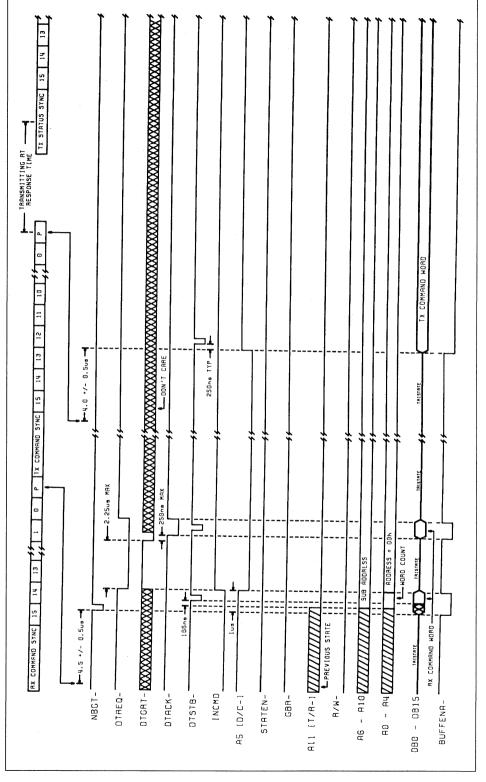

Upon initialization of power to the CT25XX Series, all registers are reset. The operation register is reset to FF80H; this setting defaults to the remote terminal mode of operation with the Busy Bit set. To enter into the Bus Control Mode of operation, bit 8 of the operation register must be asserted low. While in this mode, the upper byte (8 bits) of the operation register controls Bus Control functionality. This includes TEST/NORMAL operation, RT to RT commands, BUS selection and RETRY initialization of a faulty transaction.

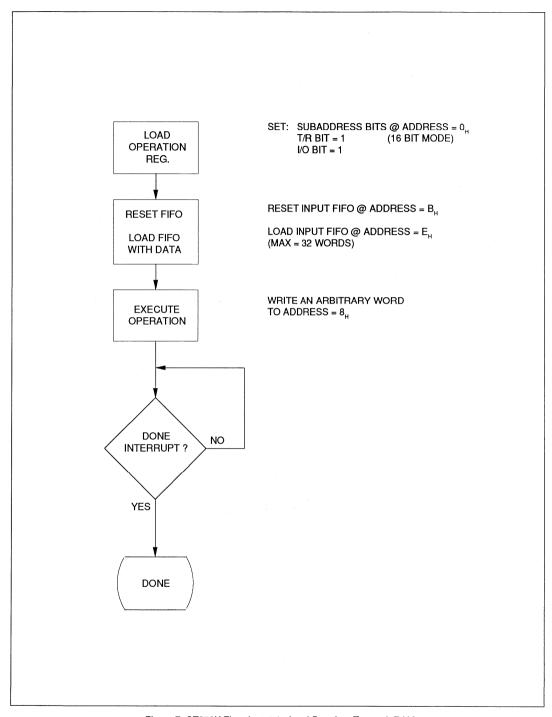

A typical Bus Control transaction would operate as follows: All areas of internal RAM that will be used for transmission are initialized by the subsystem with the desired data. To accomplish this, the subsystem will first WRITE to the INPUT buffer the number of words to be transferred. This information is now transferred to the internal RAM under control of the OPERATION register by specifying the subaddress bits 0-4, setting the T/R bit (bit 5) and I/O bit (bit 6) high. This will be executed by issuing an EXECUTE operation I/O command. When the transfer has been completed, the DONE interrupt will pulse low, and valid

data will now reside in this RAM location. Next, the subsystem will write the command word to COMMAND WORD #1 register. If it were an RT-to-RT transfer, the transmitting RT command word would be written into COMMAND WORD #2 register. The next register to be intitialized would be the OPERATION register. which controls which bus to transmit on and if retry will be an option. This information will be enacted upon when the subsystem issues a TRIGGER I/O command. The return status word from the remote terminal or status words for RT-to-RT transfers will reside in their appropriate registers upon the issuance of INT #1. If the RETRY option had been selected and a valid transfer had not occurred, the RETRY interrupt would have occurred instead of INT #1. Three retrys are the maximum number allowed. The retrys can be accomplished on the primary or secondary bus determined by proramming bits in the operation register.

A retry will be initiated if the retry bits are set in the OPERATION register. The criteria for attempting a retry is the the lack of a returned status word or returned mode data, or that 768usec has transpired since the start of the data transfer. A retry will not be executed if bits are set in the return status word(s); this is up to the subsystem to interpret the statuswword contents and to reinitiate the transfer if desired.

#### **Discrete Interrupts**

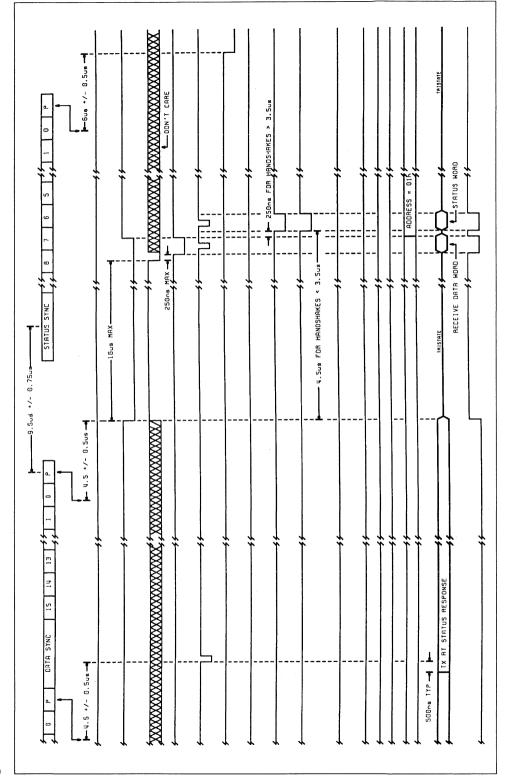

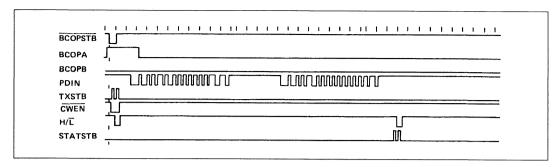

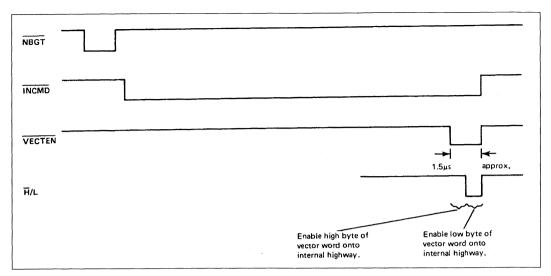

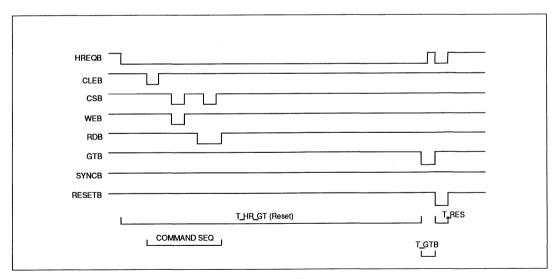

Twelve discrete interrupt output signals are available for the subsystem interface. Any or all of these may be used depending on subsystem requirements. Excluding the signal BUFF EF, all interrupts are low going pulse signals. Interrupt and status signals RESET, DBCREQ, and NBGT are 500ns wide nominally, and VECTOR is typically 1.5us wide. All remaining interrupts are nominally 160ns.

The output buffer empty flag (BUFF EF), which is a level, is also made available for subsystem use. When low, it indicates the output buffer is empty. See Table 6 for additional information.

#### **REGISTER SUMMARY**

Remote Terminal Command Word Register: This Register is utilized in the RT mode and is read only. It contains all valid received command words, i.e. transmit, receive, and mode command.

Receive Command Word Register: After the reception of a valid receive message, and the GOOD BLOCK interrupt has been issued, the Receive Command word will be transferred from the Remote Terminal Command Word Register to this register. The purpose of double buffering receive command words is to maximize the time a subsystem has to read this command since GOOD BLOCK comes at the end of the data transfer, and the next command word could overwrite the contents of the Remote Terminal Command Word Register. This is a READ ONLY register in RT mode.

**Command Word #1 Register:** This register contains the *first* command word to be transmitted during an RT to RT transfer, or the command word for a BC to RT, or RT to BC transfer. This register is a read or write register.

Vector Word/Command Word #2/ Associated Mode Data Register: This register is used to accomplish multiple functions in Bus Controller and Remote Terminal Modes. In BC Mode it will contain the second command word for (RT to RT) transfers, or Associated Mode Data that is required by certain mode codes; i.e., Sync (with data). When operated in the RT Mode, this register contains the Vector Word required by mode code Transmit Vector Word Command.

STATUS Word #1 Register: The utilization of this register in the BC mode is read only. It contains the returned status word for BC to RT, RT to BC mode, or the first returned status in RT to RT mode. At reset or the initiation of a bus transfer, the contents of this register will be set to all high, FFFFH.

Synchronize/Status Word #2/ Return Mode Data Register: In Bus Controller mode this register will either contain the second returned status word for RT to RT transfers or the returned mode data; i.e., BIT word or Vector word, Last Status word, or Last Command word. In BC mode this register is initialized to all highs, FFFFH . Unlike the other status word register, this does function in the RT mode, but is still read only in either mode. In RT mode it will contain the SYNC data word received in association with the Synchronize with Data Mode Code.

Operation Register: This register contains information provided by the subsystem to control the interface. This register sets up the mode of operation for the interface (BC or RT), selects the available options (BUS Select and Auto Retry), and contains information for reading or writing data to the Internal RAM. (See note below.) This register also provides software control of the DBCACC, SERVREQ, and SSERR bits of the status word. Following power-up master reset, bit 7 of this register will be set high. This bit corresponds to the busy bit of the Remote Terminal Status Word. The subsystem reads and writes to this register under I/O commands. The transfer functions defined by this register are executed by either of the two I/O EXECUTE Commands.

**Note:** The Internal RAM is divided into transmit or receive sections. In general, data is written to the transmit section and read from the receive section. However, either section may be read from or written to via the T/R bit in this register.

#### **SELF TEST**

The inclusion of simple wraparound selftest circuitry in the protocol section insures that a high percentage of coverage is attainable. Testing requires simple subsystem intervention. A word is first placed in the VECTOR WORD Register. Test bit 9 in the OPERATION Register is asserted low and the I/O TEST TRIGGER address is written. The LT LOCAL (Bit 10 of the Operation Register) determines if this will be an ON/OFF line test. OFF line tests are performed by the inclusion of digital multiplexers in front of the encoder, bypassing the transceiver,

providing a path to the decoder. The ON line tests are accomplished when not connected to a bus network, such as a maintenance test station, since this test utilizes the transceiver to provide the loop back path instead of the internal multiplexers. In this mode test words would appear on the bus. First, the primary bus will be tested with the data that resides in the VECTOR WORD Register. It is encoded then looped back, decoded and presented to the subsystem as a normal data transfer would be accomplished. This word will be stored in the RT Command Word Register. The secondary bus is sequentially tested after the primary bus is completed, utilizing the word residing in the VECTOR WORD Register. Upon successful completion of the test, the PASS interrupt will be asserted low.

In addition to this test of the protocol section, the subsystem data handling capability is also testable via the OPERATION Register. This is accomplished by writing a message to the INPUT FIFO Buffer; this data can be placed in any location determined by the SA0 through SA4 Bits, or in either the transmit or receive section (T/R Bit). This same data can now be transferred from this RAM location to the OUTPUT FIFO Buffer and compared with the data originally written to the INPUT FIFO Buffer. Providing this type of testing provides a high degree of functional verification .

This test implementation not only verifies MIL-STD-1553 protocol compliance (proper sync character, 16 data bits, Manchester 11 coding, odd parity, and contiguous word checking), but also the inclusion of a bit by bit comparison of transmitted data has been added. The added circuitry is used to insure that the internal functional blocks, encoder, decoder, and internal control circuitry are functioning properly. The internal data path can be verified as fault free by comparing the returned data word with the supplied data. The most effective data pattern to accomplish this is HEX AA55, since each bit is toggled (8 bit internal highway) on a high/low byte basis. Total time to complete the test is 89 microseconds. TEST ENABLE (bit 9) must remain low this entire time to ensure proper operation of the self test.

#### **USE OF A10 AND A10IN**

The standard configuration of the CT25XX Series divides the INTERNAL RAM into separate RECEIVE and TRANSMIT sections. For this configuration A10 is connected to A10IN. When A10 is high, it addresses the TRANSMIT section; when low, the RECEIVE sections. A10IN is the address input to the INTERNAL RAM.

The interface may be configured with one common section for both RECEIVE and TRANSMIT data. To configure this, A10 is not connected, and A10IN is fixed at either a logic high or low. This bit can also be controlled by the subsystem to provide double buffering of the contents of common RAM section for receive and transmit data. If A10 and A10IN are not directly connected together but gated together, then no more than 100 nsec of propogation delay should be introduced.

#### **NON-REGISTER OPERATIONAL COMMANDS**

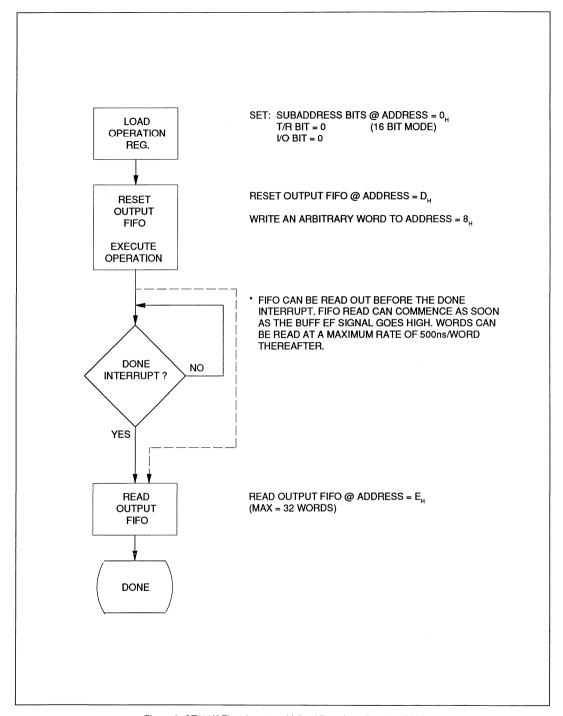

There are six operational commands that are not register read or write operations. These commands are summarized in Table 8. The two execute operations are dependent on the contents of the OPERATION register. The address codes for all the operational commands are summarized in the 8 bit and 16 bit I/O OPERATIONAL tables.

| Name             | Use                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT #1           |                                                                                                                                                                                                                                                                                                                                                                                    |

| GOOD BLOCK (RT)  | Indicates reception of a valid block of data. The RECEIVE COMMAND WORD is loaded in RCV CMD WD Register. This interrupt is issued after the new block of data is moved into the Internal RAM.                                                                                                                                                                                      |

| VALID (BC)       | Indicates that the Bus Controller has initiated and observed a valid message transfer on the 1553 data bus.                                                                                                                                                                                                                                                                        |

| INT #2           |                                                                                                                                                                                                                                                                                                                                                                                    |

| VALID TRANS (RT) | Indicates reception of a valid TRANSMIT COMMAND WORD.  The TRANSMIT COMMAND WORD is loaded in CMD WD Register.  Note: This interrupt does not necessarily indicate that the transmitted data was received by the bus controller.                                                                                                                                                   |

| INVALID (BC)     | Indicates that the Bus Controller has initiated a message transfer on the data bus, but the message traffic has been deemed invalid.                                                                                                                                                                                                                                               |

| SYNC NO DATA     | Indicates recption of a valid mode command SYNCHRONIZE WITHOUT DATA.                                                                                                                                                                                                                                                                                                               |

| SYNC W/DATA      | Indicates reception of a valid mode command SYNCHRONIZE WITH DATA. The synchronize data word is loaded into the SYNC/STAT WD #2/RMD REGISTER. This interrupt will not be issued if a word count high or low error occurs.                                                                                                                                                          |

| DONE             | This interrupt is issued in response to an I/0 command from the subsystem. In response to an I/0 load OUTPUT buffer command, it indicates that the complete 32 word message block (SUBADDRESS) has been loaded into the OUTPUT FIFO buffer. In response to an I/0 load internal RAM from INPUT FIFO buffer command, it indicates the full message (1 to 32 WORDS) has been loaded. |

|                  | TIMING a. In response to an I/0 load OUTPUT buffer: 16.5 to 33 usec.* b. In response to an I/0 load RAM from INPUT buffer: 16.5 to 33 usec for 32 WORDS*, for SHORTER LOAD OPERATIONS SUBTRACT 0.5 usec per (16 bit) word, i.e., 17 usec to 0.5 usec for single word.                                                                                                              |

|                  | *NOTE: In the unusual case where a superceding transmit command on the redundant bus occurs at the returned status time for a valid 32 word receive, simultaneously with an I/0 transfer request, the DONE interrupt may be delayed for an additional 16.5 usec.                                                                                                                   |

Table 6: Discrete Interrupts Summary

| Name      | Use                                                                                                                                                                                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

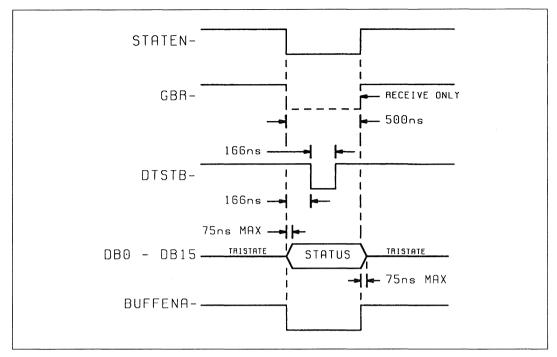

| BUFFEF    | This flag may be used to speed up read data operation in response to an I/O load OUTPUT FIFO buffer command. The BUFF EF flag will go high when the first word is loaded into the OUTPUT FIFO buffer. The word may be read at that time. Please see Figure 6. |

| MODERESET | Indicates reception of a valid RESET mode command.                                                                                                                                                                                                            |

| VECTOR    | Indicates that a transmit VECTOR mode command has been received. VECTOR DATA is transmitted from VW/CMD WD #2/AMD Register.                                                                                                                                   |

| DBCREQ    | Indicates acceptance of DYNAMIC BUS CONTROL COMMAND REQUEST.  Note: RTU will not accept valid DBC mode command unless DBCACC bit is set low in the OPERATION Register.                                                                                        |

| RETRY     | Indicates that an error has occurred in the data transfer and that a retry will be performed if the retry option is selected. If all retries that were selected fail, INVALID TRANSFER INTERRUPT would be asserted on the final failure.                      |

| SELF TEST | Indicates that the INITIATE SELF TEST mode command is being serviced.                                                                                                                                                                                         |

| PASS      | Active low pulse output signal which indicates that a sub-system initiated self-test (on-<br>or off-line) operation has been sucessfully completed. This interrupt will be issued<br>approximately 90us after the self-test operation has been triggered.     |

Table 6: Discrete Interrupts Summary (continued)

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                       |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-4 | SA BITS | SUBADDRESS BITS<br>Define SUBADDRESS MESSAGE BLOCK in INTERNAL RAM.                                                                                                                                                                                                                                                                                            |

|     |         | BIT SUBADDRESS BIT  0 SA0 (LSB)  1 SAI  2 SA2  3 SA3  4 SA4 (MSB)  These bits correspond directly to 1553B definition in the command word. Although SUBADDRESSES 00000 <sub>B</sub> and 11111 <sub>B</sub> are illegal in 1553B, message blocks specified by them are both READABLE and WRITABLE by the SUBSYSTEM. They are not accessible from the 1553B BUS. |

| 5   | T/R BIT | TRANSMIT/RECEIVE BIT points INPUT/OUTPUT OPERATIONS to either the TRANSMIT SECTION or RECEIVE SECTION of the INTERNAL RAM.                                                                                                                                                                                                                                     |

Table 7: Operation Register

| Bit | Name                          | Function                                                                                                                                                                                                                                                      |

|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | I/O BIT                       | INPUT/OUTPUT BIT DEFINES DIRECTION OF DATA TRANSFER                                                                                                                                                                                                           |

|     |                               | <ol> <li>SET HIGH: INPUT OPERATION         An EXECUTE operation will transfer the Data currently loaded in the input FIFO buffer to the specified message block (SUBADDRESS) in the internal RAM.     </li> </ol>                                             |

|     | V.                            | IF EXECUTE WITH RPT OPTION COMMAND is used, previously loaded data (i.e. data for which a load operation was previously executed) will be loaded to a new message block.                                                                                      |

|     |                               | Between 1 and 32 data words must be loaded in the input FIFO buffer when using an EXECUTE command with this bit set.                                                                                                                                          |

|     |                               | <ol> <li>SET LOW: OUTPUT OPERATION<br/>EXECUTE operation will transfer a complete block of data (32 words)<br/>to the output FIFO buffer from the specified subaddress of internal RAM.</li> </ol>                                                            |

| 7   | BUSY BIT                      | RTU BUSY<br>HIGH- BUSY<br>LOW - NOT BUSY<br>MASTER RESET SETS BIT HIGH                                                                                                                                                                                        |

| 8   | RT/BC                         | Remote Terminal/Bus Controller Bit. This line, when set HIGH, causes the hybrid to function as a Remote Terminal. When set LOW, it will function as a Bus Controller. Master reset sets this bit HIGH                                                         |

| 9   | Transaction/Test              | Transaction/Test Mode Bit. When this bit is set high, normal transactions will be handled, eg., BC to RT, RT to BC, RT to RT. If this bit is set low and a trigger transaction is issued, the self-test will be performed for the MIL-STD-1553 protocol chip. |

| 10  | LT Local                      | Loop Test Local Bit (Used in conjunction with BIT 9). This signal selects the self test path. When set LOW, the internal digital path is selected. When set HIGH, the external path, including transceivers, is selected.                                     |

| 11  | Bus Select                    | Bus Select (Bus Controller Only). When set high, Bus 1 is selected. When set LOW, the opposite bus, Bus 0 is selected.                                                                                                                                        |

| 12  | Normal/RT-RT                  | Normal/Remote Terminal-Remote Terminal Bit. When set HIGH, BC to RT and RT to BC transfers are performed. When set LOW RT to RT transfers are performed. Two command words are required and two returned status words will be expected.                       |

| 13  | SERV REQ/<br>Auto-Retry (LSB) | Service Request/Auto-Retry (LSB) Bit.  RT MODE: A LOW in this bit will cause the service request bit in the status word to be set.  BC MODE: This is the LSB of the Auto-Retry options. See table on page 15, Bit 14                                          |

Table 7: Operation Register (continued)

| Bit | Name             | Function    |                                       |                     |                      |  |  |  |

|-----|------------------|-------------|---------------------------------------|---------------------|----------------------|--|--|--|

| 14  | SERR             | Subsystem E | Subsystem Error/Auto-Retry (MSB) Bit. |                     |                      |  |  |  |

|     | Auto-Retry (MSB) |             |                                       |                     | Subsystem Error      |  |  |  |

|     | • • • •          |             | Bit in the stat                       | us word to be se    | et.                  |  |  |  |

|     |                  | BC MODE:    | This is the MS                        | SB of the Auto-F    | Retry options.       |  |  |  |

|     |                  | AUTO-R      | ETRY OPERA                            | TIONS               |                      |  |  |  |

|     |                  | Options     | selected:                             | If transacti        | on initiated on bus: |  |  |  |

|     |                  | Bit 14      | Bit 13                                | Primary             | Secondary            |  |  |  |

|     |                  | 0           | 0                                     | No Retry            | No Retry             |  |  |  |

|     |                  | 0           | 1                                     | S                   | P                    |  |  |  |

|     |                  | 1           | 0                                     | P/S                 | P/P                  |  |  |  |

|     |                  | . 1         | 1                                     | P/S/S               | P/P/P                |  |  |  |

| 15  | DBCACC/          | Dynamic Bus | S Control Accer                       | ot/Auto-Retry Bu    | s Bit.               |  |  |  |

|     | Auto-Retry       | RT MODE:    |                                       |                     | subsystem is able    |  |  |  |

|     | Other Bus        |             |                                       | trol of the bus, it |                      |  |  |  |

|     |                  | BC MODE:    |                                       | d be HIGH if an     |                      |  |  |  |

|     |                  |             | is to be retrie                       | d according to the  | ne selected auto-    |  |  |  |

|     |                  |             | retry option lis                      |                     |                      |  |  |  |

Table 7: Operation Register (continued)

| Operation                  | Function                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                      | RESET INPUT/OUTPUT BUFFERS  This command clears both the input and output FIFO buffers. The BUFF EF flag will go low indicating the output buffer is empty.                                                                                                                                                                                                                   |

| READ OUTPUT<br>DATA BUFFER | READ OUTPUT FIFO READS the data moved from the INTERNAL RAM in response to an UNLOAD execute operation. The order of the data words corresponds to the same order that they would be received on the 1553B bus. That is the first data word read is the first data word following the COMMAND word. In the 8 bit mode the HIGH BYTE is read FIRST.                            |

| WRITE INPUT<br>DATA BUFFER | WRITE INPUT FIFO WRITES the data that will be moved into the INTERNAL RAM in response to a LOAD execute operation. The order of the data words corresponds to the same order that they would be transmitted on the 1553B bus. That is the first data word written is the first data word transmitted following the status word. In 8 bit mode the HIGH BYTE is written FIRST. |

| EXECUTE OP.                | EXECUTES OPERATION SPECIFIED IN OPERATION REGISTER  1. I/O BIT HIGH Data currently in INPUT FIFO BUFFER is loaded into the INTERNAL RAM block specified by the T/R BIT and SUBADDRESS FIELD of the OPERATION REGISTER. The INPUT BUFFER must have at least one data word. The DONE interrupt is pulsed when the operation is completed.                                       |

|                            | 2. I/O BIT LOW<br>An entire block of data (32 words) specified by the T/R and the SUBADDRESS<br>field of the OPERATION REGISTER is unloaded from the INTERNAL RAM into the<br>OUTPUT FIFO BUFFER. The BUFF EF Flag goes high when the first data word is<br>moved into the OUTPUT BUFFER. The DONE interrupt is pulsed when the<br>complete message has been moved.           |

Table 8: Non-Register Operational Commands

#### EXECUTE OP. EXECUTES OPERATION SPECIFIED IN OPERATION REGISTER WITH WITH RPT OPTION REPEAT OPTION 1. I/O BIT HIGH Data previously written into the INPUT BUFFER is loaded into a new INTERNAL RAM block specified by the T/R and SUBADDRESS field of the OPERATION REGISTER. This operation allows a block of data loaded in the INPUT BUFFER to be repeatedly copied into multiple subaddresses of the INTERNAL RAM without the subsystem having to reload the data. The DONE interrupt is pulsedwwhen the operation is completed. The intent of the operation is to minimize the time required to initialize the INTERNAL RAM. 2. I/O BIT LOW Operation identical to EXECUTE OP, WITHOUT RPT opion. TRIGGER TRANSACTION TRANSACTION/TEST TRIGGER This signal executes the desired Bus Controller Function or test of the TRIGGER TEST protocol section determined by the Operation Register.

Table 8: Non-Register Operational Commands (continued)

| Operation                           | RD | WT | DS | AD3 | AD2 | AD1 | AD  |

|-------------------------------------|----|----|----|-----|-----|-----|-----|

| BC AND RT MODE                      |    |    |    |     |     |     |     |

| No Operation-I/O Bus Tri-stated     | x  | x  | 1  | х   | X   | X   | x   |

| Read Operation Reg. High Byte       | *P | 1  | 0  | 0   | 0   | 0   | 1   |

| Read Operation Reg. Low Byte        | Р  | 1  | 0  | 0   | 0   | 0   | 0   |

| Write Operation Reg. High Byte      | 1  | Р  | 0  | 0   | 0   | 0   | - 1 |

| Write Operation Reg. Low Byte       | 1  | Р  | 0  | 0   | 0   | 0   | 0   |

| Read Output FIFO (High Byte First)  | Р  | 1  | 0  | 1   | 1 . | 1   | 0   |

| Write Input FIFO (High Byte First)  | 1  | Р  | 0  | 1   | 1   | 1   | 0   |

| Execute Operation (Load/Unload RAM) | 1  | Р  | 0  | 1   | 0   | 0   | 0   |

| Execute Operation with Repeat       | 1  | Р  | 0  | 1   | 0   | 1   | 0   |

| Reset Input FIFO                    | 1  | Р  | 0  | 1   | 0   | 1   | 1   |

| Reset Output FIFO                   | 1  | Р  | 0  | 1   | 1   | 0   | - 1 |

| Reset Input and Output FIFOS        | 1  | Р  | 0  | 1   | 1   | 0   | 0   |

| Frigger Test                        | 1  | Р  | 0  | 1   | 0   | 0   | 1   |

| RT MODE ONLY                        |    |    |    |     |     |     |     |

| Read RT Command Word Reg. High Byte | P  | 1  | 0  | Ó   | 1   | 0   | 1   |

| Read RT Command Word Reg. LowByte   | Р  | 1  | 0  | 0   | 1 . | 0   | 0   |

| Read Receive Command Reg. High Byte | P  | 1  | 0  | 0   | 0   | 1   | 1   |

| Read Receive Command Reg. LowByte   | Р  | 1  | 0  | 0   | 0   | 1   | 0   |

| Read SYNC Data Reg. High Byte       | Р  | 1  | 0  | 0   | 1   | 1   | 1   |

| Read SYNC Data Reg. Low Byte        | Р  | 1  | 0  | 0   | 1   | 1   | 0   |

| Vrite Vector Word Reg. High Byte    | 1  | Р  | 0  | 0   | 1   | 1   | 1   |

| Vrite Vector Word Reg. Low Byte     | 1  | Р  | 0  | 0   | 1   | 1   | 0   |

\*P = Active Low Strobe

Note: When operating in 8-bit mode it is recommended that FIFO access be confined to *even* numbers of Read or Write operations *only*. Failure to conform to this can result in incorrect data being transferred to internal RAM.

Table 9: CT2525/26/27 8-Bit Mode I/O Operations

| BC MODE ONLY                             |   |   |     |   |   |   |   |

|------------------------------------------|---|---|-----|---|---|---|---|

| Read Status Word #1 Reg. High Byte       | P | 1 | 0   | 0 | 0 | 1 | 1 |

| Read Status Word #1 Reg. Low Byte        | Р | 1 | 0   | 0 | 0 | 1 | 0 |

| Read Status Word #2/RMD Reg. High Byte   | Р | 1 | . 0 | 0 | 1 | 1 | 1 |

| Read Status Word #2/RMD Reg. Low Byte    | Р | 1 | 0   | 0 | 1 | 1 | 0 |

| Write Command Word #1 Reg. High Byte     | 1 | Р | 0   | 0 | 0 | 1 | 1 |

| Write Command Word #1 Reg. Low Byte      | 1 | Р | 0   | 0 | 0 | 1 | 0 |

| Write Command Word #2/AMD Reg. High Byte | 1 | Р | 0   | 0 | 1 | 1 | 1 |

| Write Command Word #2/AMD Reg. Low Byte  | 1 | Р | 0   | 0 | 1 | 1 | 0 |

| Trigger Transaction                      | 1 | Р | 0   | 1 | 0 | 0 | 1 |

Table 9: CT2525/26/27 8-Bit Mode I/O Operations (continued)

| Operation                           | RD   | WT       | DS       | AD3 | AD2 | AD1 | AD0 |

|-------------------------------------|------|----------|----------|-----|-----|-----|-----|

| RT AND BC MODE                      |      |          |          |     |     |     |     |

| No Operation - I/O Bus Tri-Stated   | x    | X        | 1        | x   | x   | x   | ×   |

| Read Operation Register             | *P   | 1        | 0        | 0   | 0   | 0   | 0   |

| Write Operation Register            | 1    | Р        | 0        | 0   | 0   | 0   | 0   |

| Execute Operation (Load/Unload Ram) | 1    | Р        | 0        | 1   | 0   | 0   | 0   |

| Execute Operation with Repeat       | 1    | Р        | 0        | 1   | 0   | 1   | 0   |

| Read Output FIFO                    | Р    | 1        | 0        | 1   | 1   | 1.  | 0   |

| Write Input FIFO                    | 1    | Р        | 0        | 1   | 1   | 1   | 0   |

| Reset Input FIFO                    | 1    | Р        | 0        | 1   | 0   | 1   | 1   |

| Reset Output FIFO                   | 1    | Р        | 0        | 1   | 1   | 0   | 1   |

| Reset Input and Output FIFO         | 1    | Р        | 0        | 1   | 1   | 0   | 0   |

| Trigger Test                        | 1    | Р        | 0        | 1   | 0   | 0   | 1   |

| RT MODE ONLY                        |      |          |          |     |     |     |     |

| Read RT Command Word Register       | Р    | 1        | 0        | 0   | 1   | 0   | 0   |

| Read Receive Command Register       | Р    | 1        | 0        | 0   | 0   | 1   | 0   |

| Read SYNC Data Register             | Р    | 1        | 0        | 0   | 1   | 1   | 0   |

| Write Vector Word Register          | 1    | Р        | 0        | 0   | 1   | 1   | 0   |

| BC MODE ONLY                        |      |          |          |     |     |     |     |

| Read Status Word #1 Register        | Р    | 1        | 0        | 0   | 0   | 1   | 0   |

| Read Status Word #2/RMD Register    | Р    | 1        | 0        | 0   | 1   | 1   | 0   |

| Write Command Word #1 Register      | 1    | Р        | 0        | 0   | 0   | 1   | 0   |

| Write Command Word #2/AMD Register  | 1    | Р        | 0        | 0   | 1   | 1   | 0   |

| Trigger Transaction                 | 1    | Р        | 0        | 1   | 0   | 0   | 1   |

|                                     | *P = | Active L | ow Strol | be  |     |     |     |

Table 10: CT2525/26/27 16-Bit Mode I/O Operations

| Flat Pack                  | Plug In                    | Signal Name                                              | Description                                                                                                                                                                                                    |     |

|----------------------------|----------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 16<br>85<br>2<br>34<br>78  | 16<br>87<br>2<br>34<br>80  | V <sub>DD</sub><br>V <sub>DD</sub><br>GND<br>CASE<br>GND | Digital Supply Voltage<br>Digital Supply Voltage<br>Digital Grounds<br>Case Connection<br>Digital Grounds                                                                                                      |     |

| 38<br>44<br>43<br>39<br>41 | 38<br>44<br>43<br>39<br>41 | VccL (A)<br>VEE (A)<br>Vcc (A)<br>GND (A)<br>GND (A)     | Transceiver A +5VDC Supply Voltage Transceiver A -15VDC Supply Voltage Transceiver A +15VDC Supply Voltage Transceiver A Analog Ground Transceiver A Digital Ground                                            |     |

| 51<br>45<br>46<br>50<br>48 | 53<br>47<br>48<br>52<br>50 | VccL (B)<br>VEE (B)<br>Vcc (B)<br>GND (B)<br>GND (B)     | Transceiver B +5VDC Supply Voltage Transceiver B -15VDC Supply Voltage Transceiver B +15VDC Supply Voltage Transceiver B Analog Ground Transceiver B Digital Ground                                            |     |

| 79<br>80<br>81<br>82       | 81<br>82<br>83<br>84       | $AD_0$ $AD_1$ $AD_2$ $AD_3$                              | Address Inputs $AD_0$ - LSB $AD_3$ - MSB These four signals provide the address codes that control the operation of the interface.                                                                             |     |

| 83                         | 85                         | A10 IN                                                   | A10IN is the address input to the internal RAM.                                                                                                                                                                |     |

| 84                         | 86                         | A10 OUT                                                  | A10 OUT buffered TX/RX bit when tied to A10IN segregates the 2k by 16 RAM into two 1k by 16 blocks of memory: one for Receive, the other for Transmit Data.                                                    |     |

| 23                         | 23                         | BCSTEN                                                   | Broadcast Enable. When low, the recognition of Broadcast Command is prevented on the specified bus.                                                                                                            | . * |

| 25                         | 25                         | BIT DECODE                                               | Built-In Test Decode. When held low, prevents resetting TXTO Bit, HSFAIL Bit, and LTFAIL Bit in the Bit Word (as well as TF and SSF Bits in the Status Word) upon receipt of a Transmit Bit Word Mode Command. |     |

| 57                         | 59                         | BUFF EF                                                  | Buffer Empty Flag - goes low when the output FIFO Buffer is empty. Will transition to the high state when the first word appears in the Buffer.                                                                |     |

Table 11: Pin Numbers - CT2525

| Flat Pack      | Plug In        | Signal Name                                           | Description                                                                                                                                                                                                      |  |  |

|----------------|----------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1              | 1              | CLOCK                                                 | 6 MHz Master Clock.                                                                                                                                                                                              |  |  |

| 42             | 42             | DATA CHA                                              | DATA CHANNEL A. (BUS 0). This is the combined signals, RX Data In and TX Data Out, that connect to the IN phase primary terminal of the Bus Transformer.                                                         |  |  |

| 40             | 40             | DATA CHA                                              | DATA CHANNEL A. (BUS 0) This is the combined signals RX Data In and TX Data Out, that connect to the OUT of phase primary terminal of the Bus Transformer.                                                       |  |  |

| 47             | 49             | DATA CHB                                              | Same as DATA CHA, except for Channel B. (BUS 1).                                                                                                                                                                 |  |  |

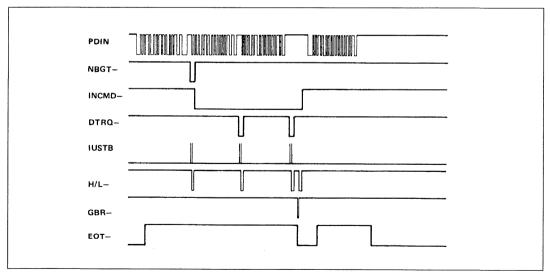

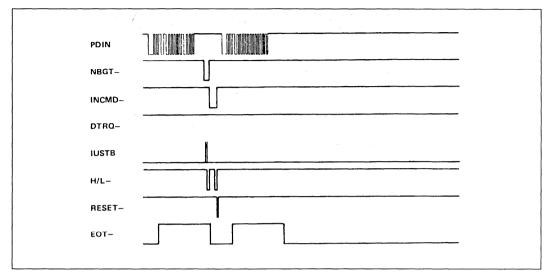

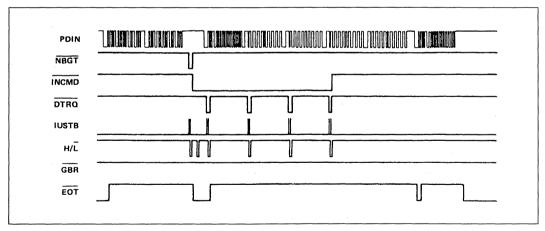

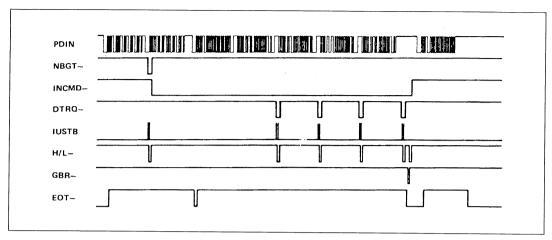

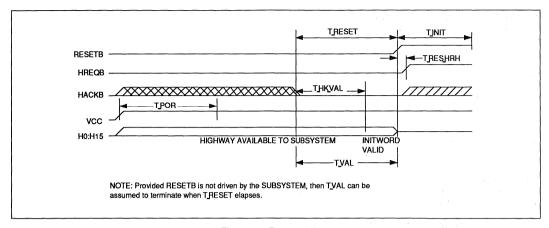

| 49             | 51             | DATA CHB                                              | Same as DATA CHA, except for Channel B. (BUS 1).                                                                                                                                                                 |  |  |